R01UH0823EJ0100 Rev.1.00 Page 406 of 1823

Jul 31, 2019

RX23W Group 19. Data Transfer Controller (DTCa)

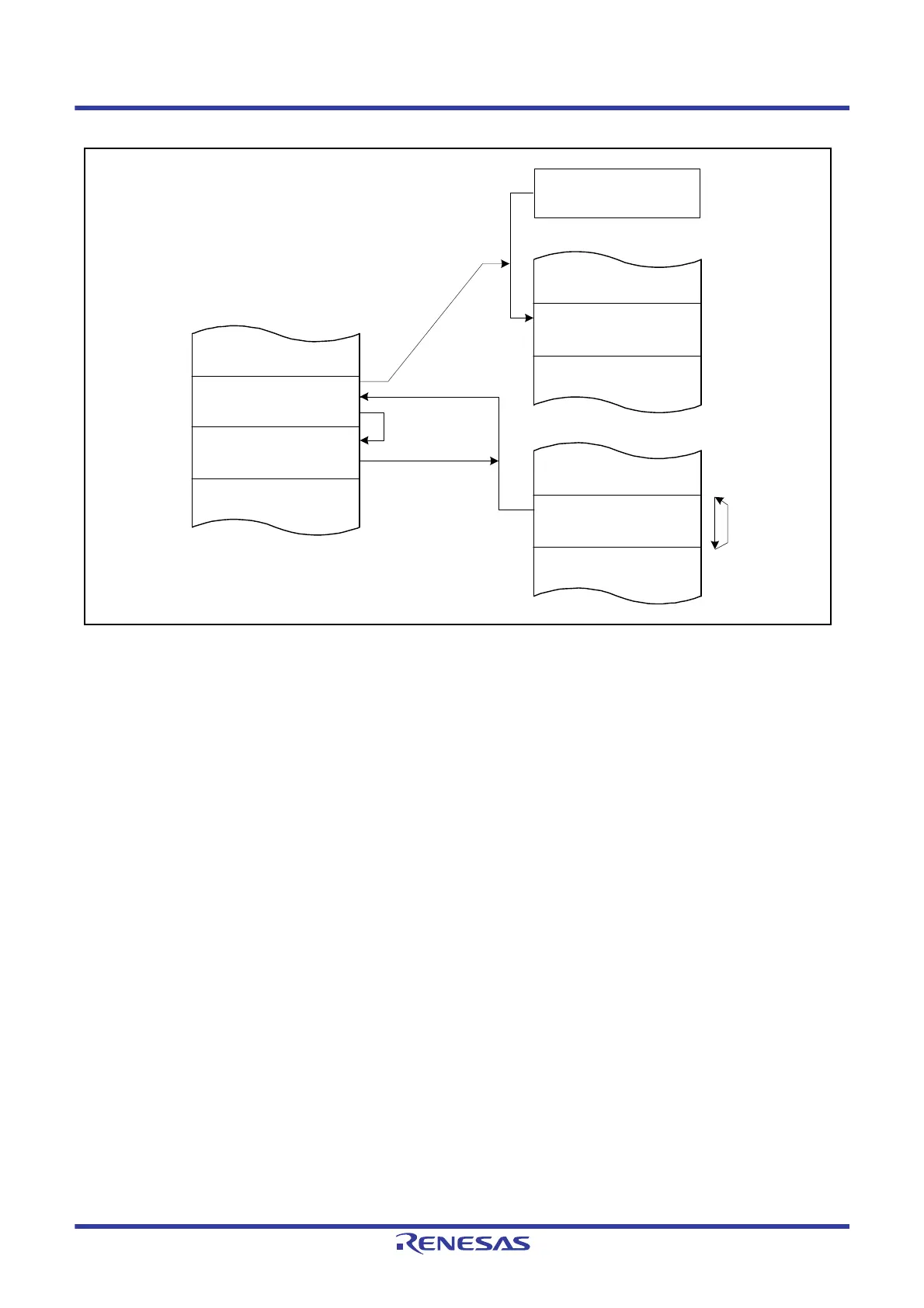

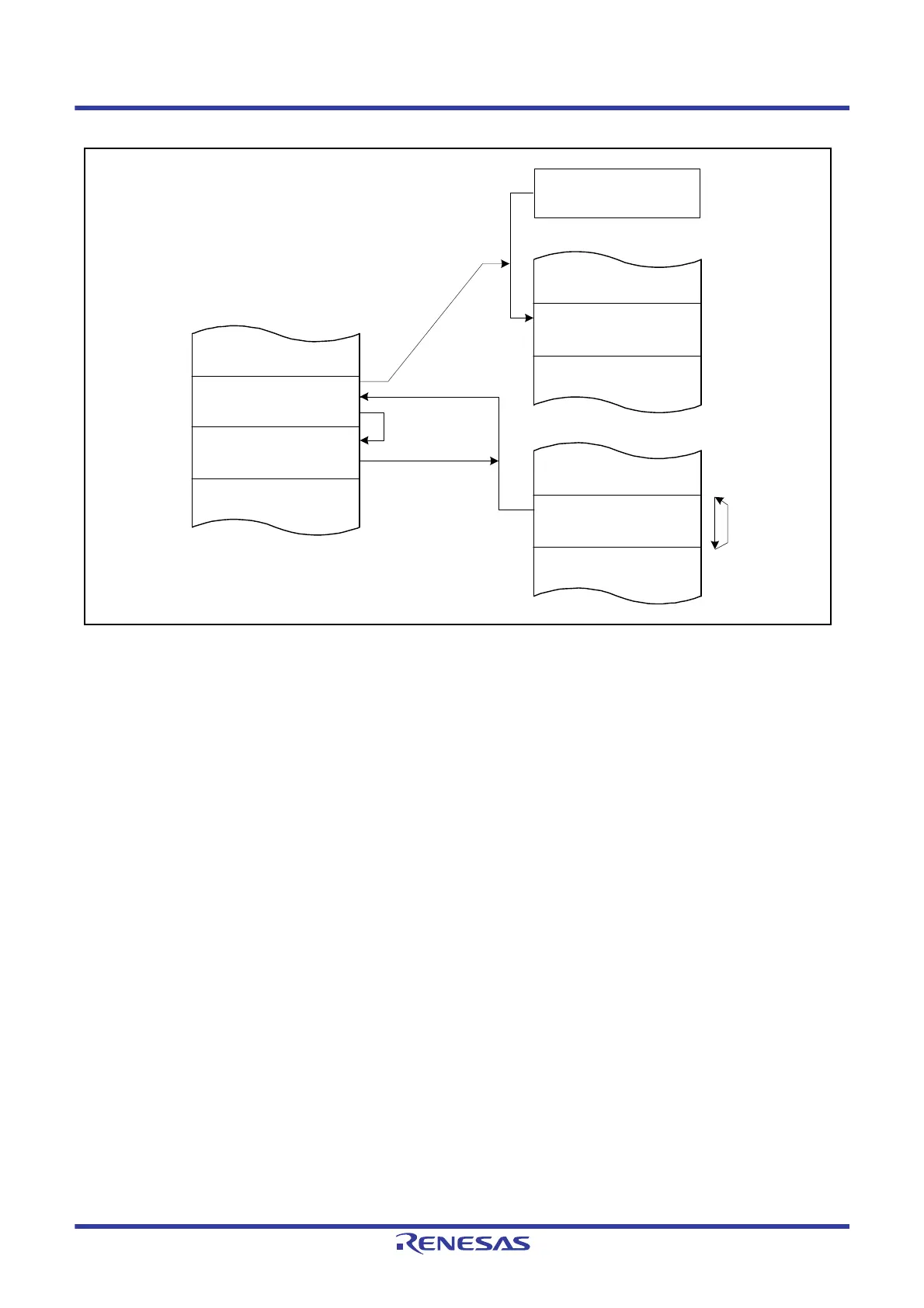

Figure 19.15 Chain Transfer When the Counter is 0

19.7 Interrupt Source

When the DTC has finished data transfer of specified count or when data transfer with the MRB.DISEL bit set to 1 (an

interrupt request to the CPU is generated each time the data transfer is performed) has been completed, an interrupt to the

CPU is generated by the DTC trigger source. Such interrupts to the CPU are controlled according to the PSW.I bit

(interrupt enable) of the CPU, the PSW.IPL[3:0] bits (processor interrupt priority level), and the priority level of the

interrupt controller.

19.8 Event Link

The DTC outputs an event signal on completing data transfer in response to one request.

Transfer information allocated in

the on-chip memory space

Chain transfer

(counter = 0)

Input circuit

Input buffer

First data transfer

Transfer information

Second data transfer

Transfer information

Upper 8 bits of DAR

Loading...

Loading...