R01UH0823EJ0100 Rev.1.00 Page 841 of 1823

Jul 31, 2019

RX23W Group 31. Independent Watchdog Timer (IWDTa)

31.2.4 IWDT Reset Control Register (IWDTRCR)

There are some restrictions on writing to the IWDTRCR register. For details, refer to section 31.3.2, Control over

Writing to the IWDTCR, IWDTRCR, and IWDTCSTPR Registers

.

In auto-start mode, the IWDTRCR register setting are disabled, and the settings in option function select register 0

(OFS0) are enabled. The bit setting mode to the IWDTRCR register can also be made in the OFS0 register. For details,

refer to

section 31.3.8, Correspondence between Option Function Select Register 0 (OFS0) and IWDT

Registers

.

Address(es): IWDT.IWDTRCR 0008 8036h

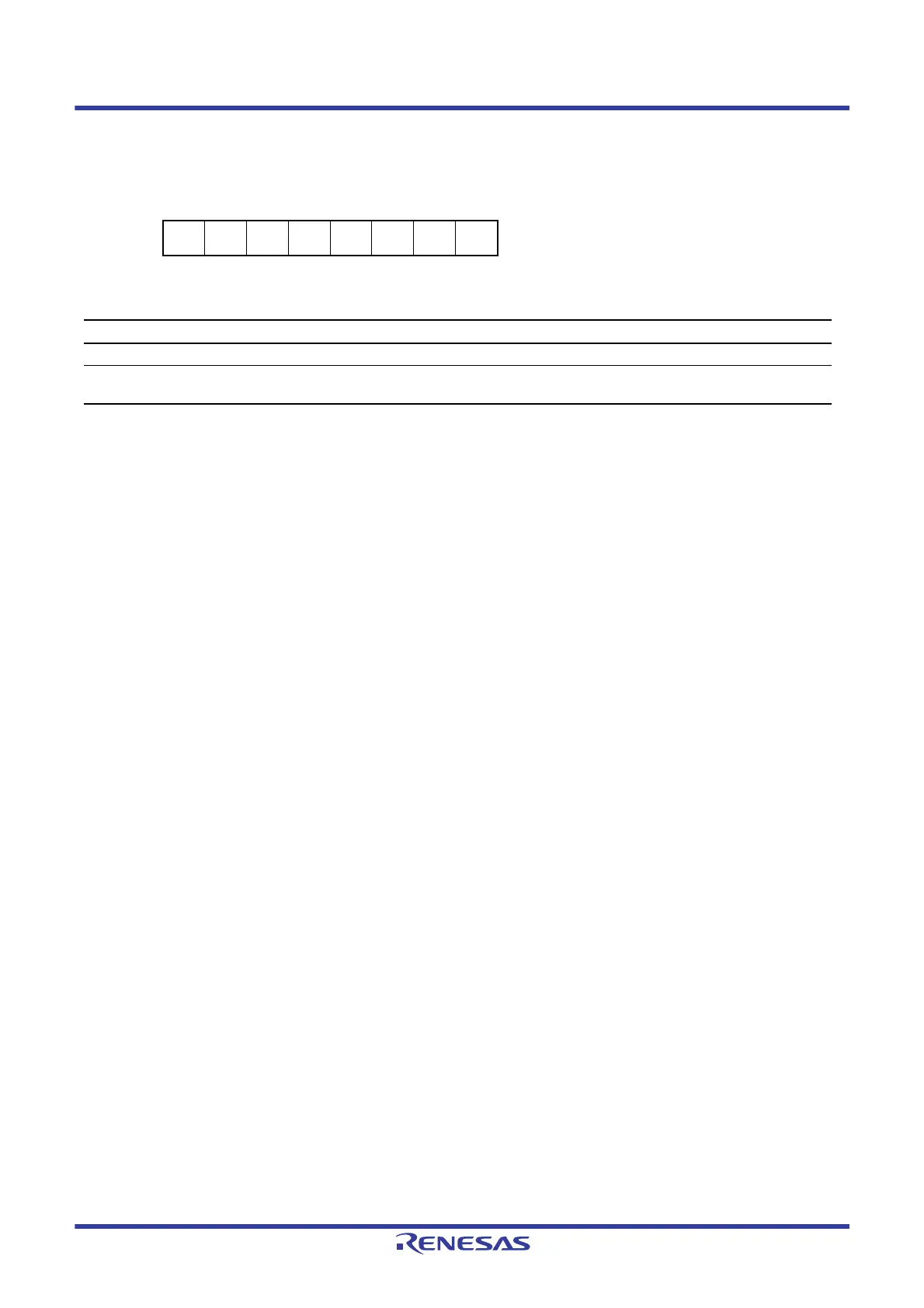

b7 b6 b5 b4 b3 b2 b1 b0

RSTIR

QS

———————

Value after reset:

10000000

Bit Symbol Bit Name Description R/W

b6 to b0 — Reserved These bits are read as 0. Writing to these bits has no effect. R

b7 RSTIRQS Reset Interrupt Request Select 0: Non-maskable interrupt request output is enabled.

1: Reset output is enabled.

R/W

Loading...

Loading...