R01UH0823EJ0100 Rev.1.00 Page 88 of 1823

Jul 31, 2019

RX23W Group 2. CPU

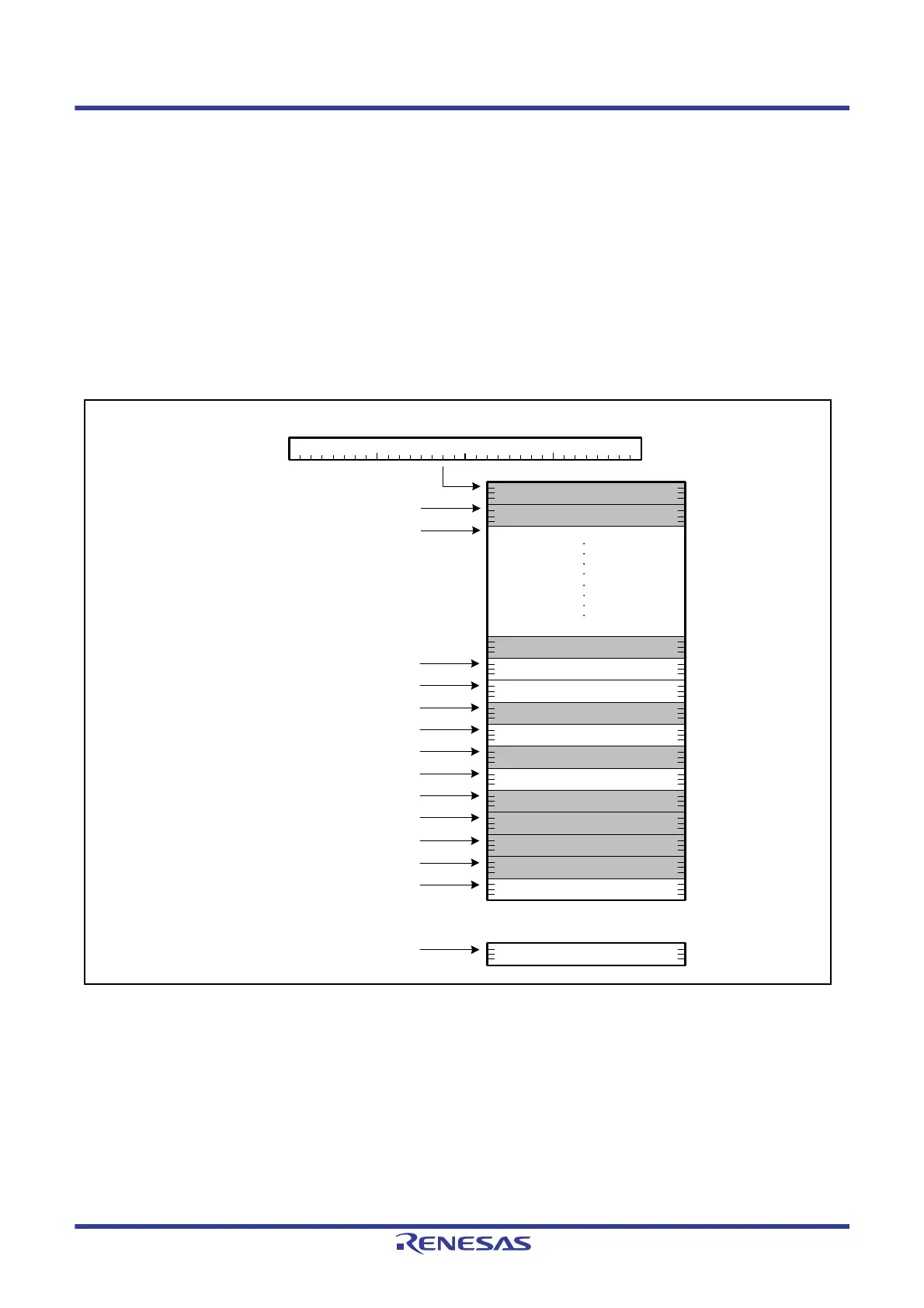

2.6 Vector Table

There are two types of vector table: exception and interrupt. Each vector in the vector table consists of four bytes and

specifies the address where the corresponding exception handling routine starts.

2.6.1 Exception Vector Table

In the exception vector table, the individual vectors for the privileged instruction exception, access exception, undefined

instruction exception, floating-point exception, and non-maskable interrupt are allocated to the 124-byte area where the

value indicated by the exception table register (EXTB) is used as the starting address (ExtBase). The reset vector is

always allocated to FFFFFFFCh, regardless of the value of the exception vector table.

Figure 2.8 shows the exception vector table.

Figure 2.8 Exception Vector Table

(Reserved)

(Reserved)

(Reserved)

EXTB

ExtBase + 04h

(Reserved)

(Reserved)

Privileged instruction exception

Access exception

(Reserved)

Undefined instruction exception

(Reserved)

Floating-point exception

(Reserved)

ExtBase

b31 b0

Value after reset: FFFFFF80h

ExtBase + 08h

ExtBase + 50h

ExtBase + 54h

ExtBase + 58h

ExtBase + 5Ch

ExtBase + 60h

ExtBase + 64h

ExtBase + 68h

ExtBase + 6Ch

Reset

Non-maskable interrupt

ExtBase + 70h

ExtBase + 74h

ExtBase + 78h

FFFFFFCh

(Reserved)

Loading...

Loading...