R01UH0823EJ0100 Rev.1.00 Page 1231 of 1823

Jul 31, 2019

RX23W Group 36. CAN Module (RSCAN)

36.2.45 Transmit/Receive FIFO Control Register 0L (CFCCL0)

CFE Bit (Transmit/Receive FIFO Buffer Enable)

Setting this bit to 1 makes transmit/receive FIFO buffers available.

When this bit is set to 0 in transmit mode, if a message in the transmit/receive FIFO buffer is being transmitted or to be

transmitted next, the transmit/receive FIFO buffer becomes empty after completion of transmission, CAN bus error

detection, or arbitration lost. In other cases or in receive mode, the transmit/receive FIFO buffer becomes empty

immediately.

Address(es): RSCAN0.CFCCL0 000A 8350h

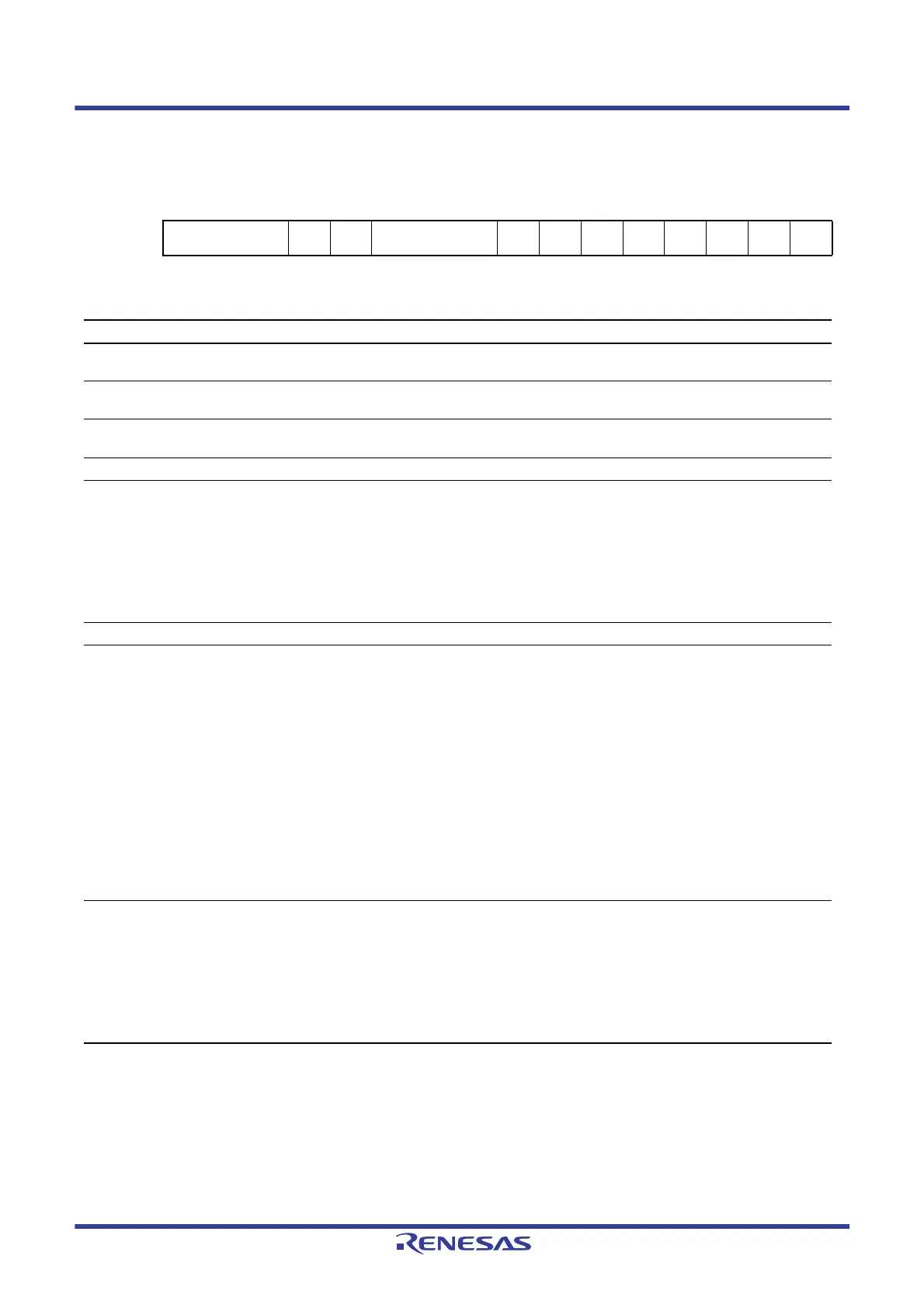

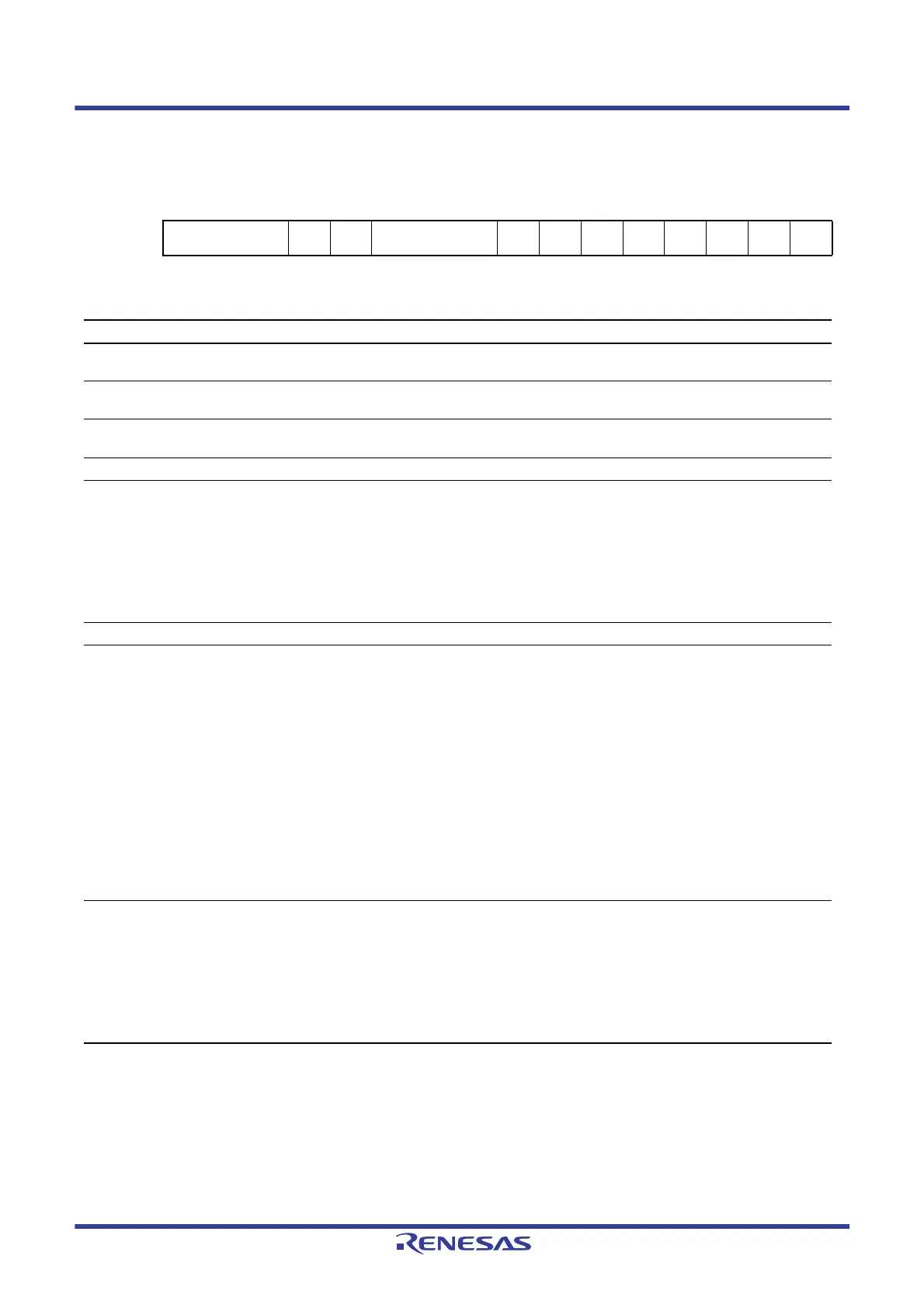

b15 b14 b13 b12 b11 b10 b9 b8 b7 b6 b5 b4 b3 b2 b1 b0

CFIGCV[2:0] CFIM— CFDC[2:0] —————CFTXIE

CFRXI

E

CFE

Value after reset:

0000000000000000

Bit Symbol Bit Name Description R/W

b0 CFE Transmit/Receive FIFO Buffer

Enable

0: No transmit/receive FIFO buffer is used.

1: Transmit/receive FIFO buffers are used.

R/W

b1 CFRXIE Transmit/Receive FIFO Receive

Interrupt Enable

0: Transmit/receive FIFO receive interrupt is disabled.

1: Transmit/receive FIFO receive interrupt is enabled.

R/W

b2 CFTXIE Transmit/Receive FIFO

Transmit Interrupt Enable

0: Transmit/receive FIFO transmit interrupt is disabled.

1: Transmit/receive FIFO transmit interrupt is enabled.

R/W

b7 to b3 — Reserved These bits are read as 0. The write value should be 0. R/W

b10 to b8 CFDC[2:0] Transmit/Receive FIFO Buffer

Depth Configuration

b10 b8

0 0 0: 0 messages

0 0 1: 4 messages

0 1 0: 8 messages

0 1 1: 16 messages

1 0 0: Setting prohibited

1 0 1: Setting prohibited

1 1 0: Setting prohibited

1 1 1: Setting prohibited

R/W

b11 — Reserved This bit is read as 0. The write value should be 0. R/W

b12 CFIM Transmit/Receive FIFO Interrupt

Source Select

0:

Receive mode

When the number of received messages has met the

condition set by the CFIGCV[2:0] bits, a FIFO receive

interrupt request is generated.

Transmit mode

When the buffer becomes empty upon completion of

message transmission, a FIFO transmit interrupt request

is generated.

1:

Receive mode

A FIFO receive interrupt request is generated each time a

message has been received.

Transmit mode

A FIFO transmit interrupt request is generated each time a

message has been transmitted.

R/W

b15 to b13 CFIGCV[2:0] Transmit/Receive FIFO Receive

Interrupt Request Timing Select

b15 b13

0 0 0: When FIFO is 1/8 full.

0 0 1: When FIFO is 2/8 full.

0 1 0: When FIFO is 3/8 full.

0 1 1: When FIFO is 4/8 full.

1 0 0: When FIFO is 5/8 full.

1 0 1: When FIFO is 6/8 full.

1 1 0: When FIFO is 7/8 full.

1 1 1: When FIFO is full.

R/W

Loading...

Loading...