R01UH0823EJ0100 Rev.1.00 Page 495 of 1823

Jul 31, 2019

RX23W Group 23. Multi-Function Timer Pulse Unit 2 (MTU2a)

23.2.7 Timer Input Capture Control Register (TICCR)

The MTU has one TICCR register for MTU1.

The TICCR register specifies input capture conditions when counters MTU1.TCNT and MTU2.TCNT are cascaded.

Address(es): MTU1.TICCR 000D 0B90h

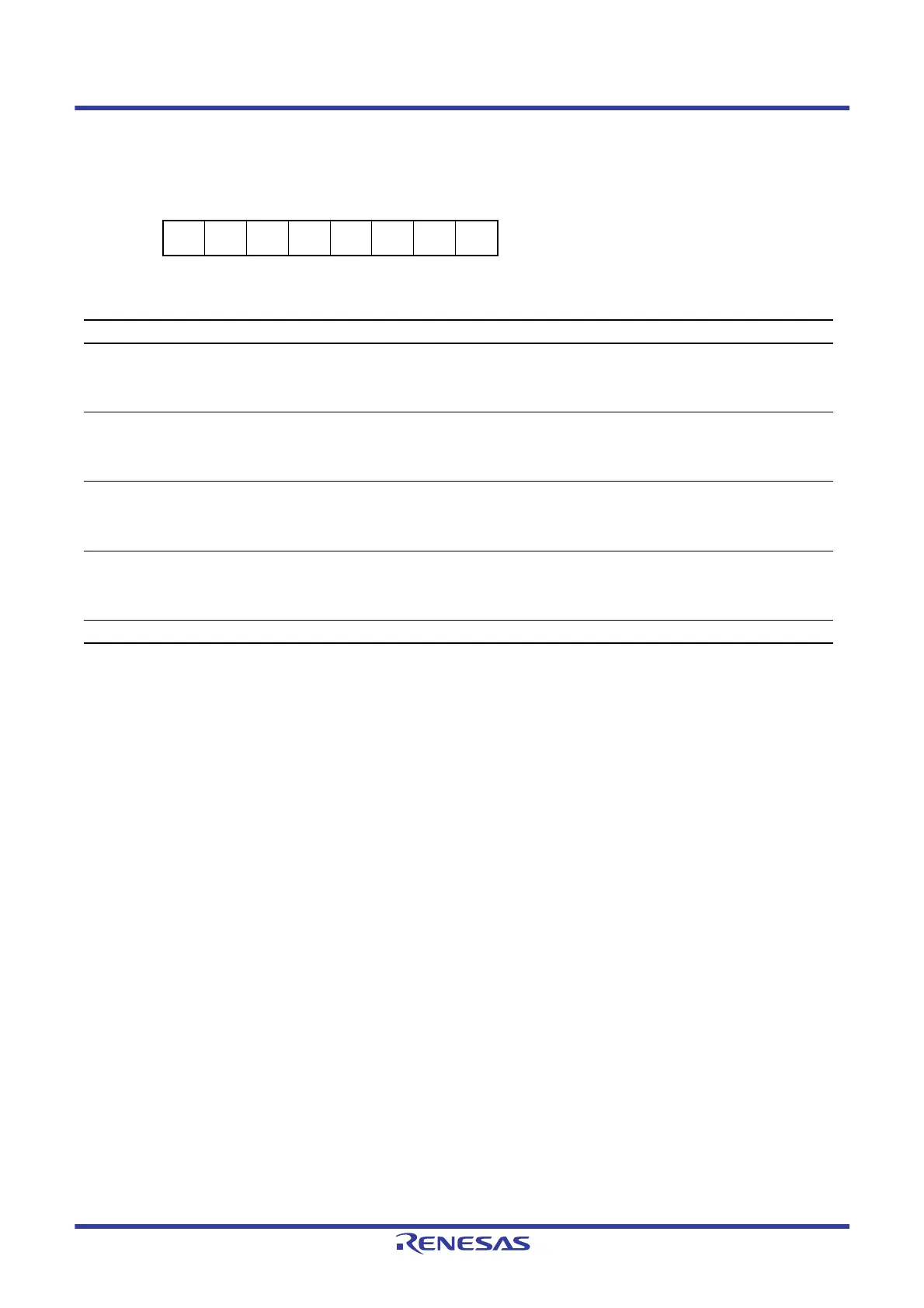

b7 b6 b5 b4 b3 b2 b1 b0

————I2BEI2AEI1BEI1AE

Value after reset:

00000000

Bit Symbol Bit Name Description R/W

b0 I1AE Input Capture Enable 0: Does not include the MTIOC1A pin in the MTU2.TGRA input capture

conditions

1: Includes the MTIOC1A pin in the MTU2.TGRA input capture

conditions

R/W

b1 I1BE Input Capture Enable 0: Does not include the MTIOC1B pin in the MTU2.TGRB input capture

conditions

1: Includes the MTIOC1B pin in the MTU2.TGRB input capture

conditions

R/W

b2 I2AE Input Capture Enable 0: Does not include the MTIOC2A pin in the MTU1.TGRA input capture

conditions

1: Includes the MTIOC2A pin in the MTU1.TGRA input capture

conditions

R/W

b3 I2BE Input Capture Enable 0: Does not include the MTIOC2B pin in the MTU1.TGRB input capture

conditions

1: Includes the MTIOC2B pin in the MTU1.TGRB input capture

conditions

R/W

b7 to b4 — Reserved These bits are read as 0. The write value should be 0. R/W

Loading...

Loading...