R01UH0823EJ0100 Rev.1.00 Page 609 of 1823

Jul 31, 2019

RX23W Group 23. Multi-Function Timer Pulse Unit 2 (MTU2a)

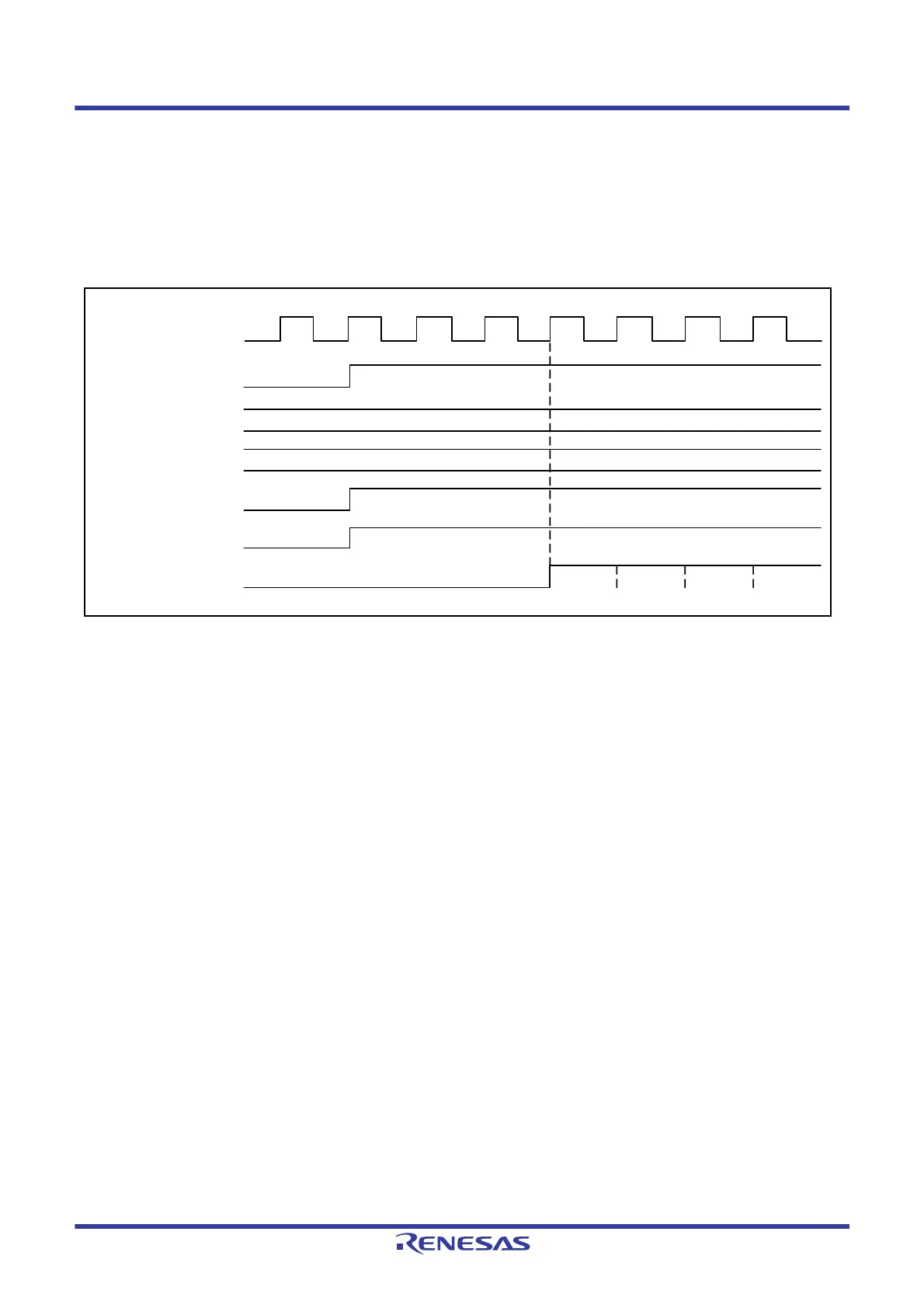

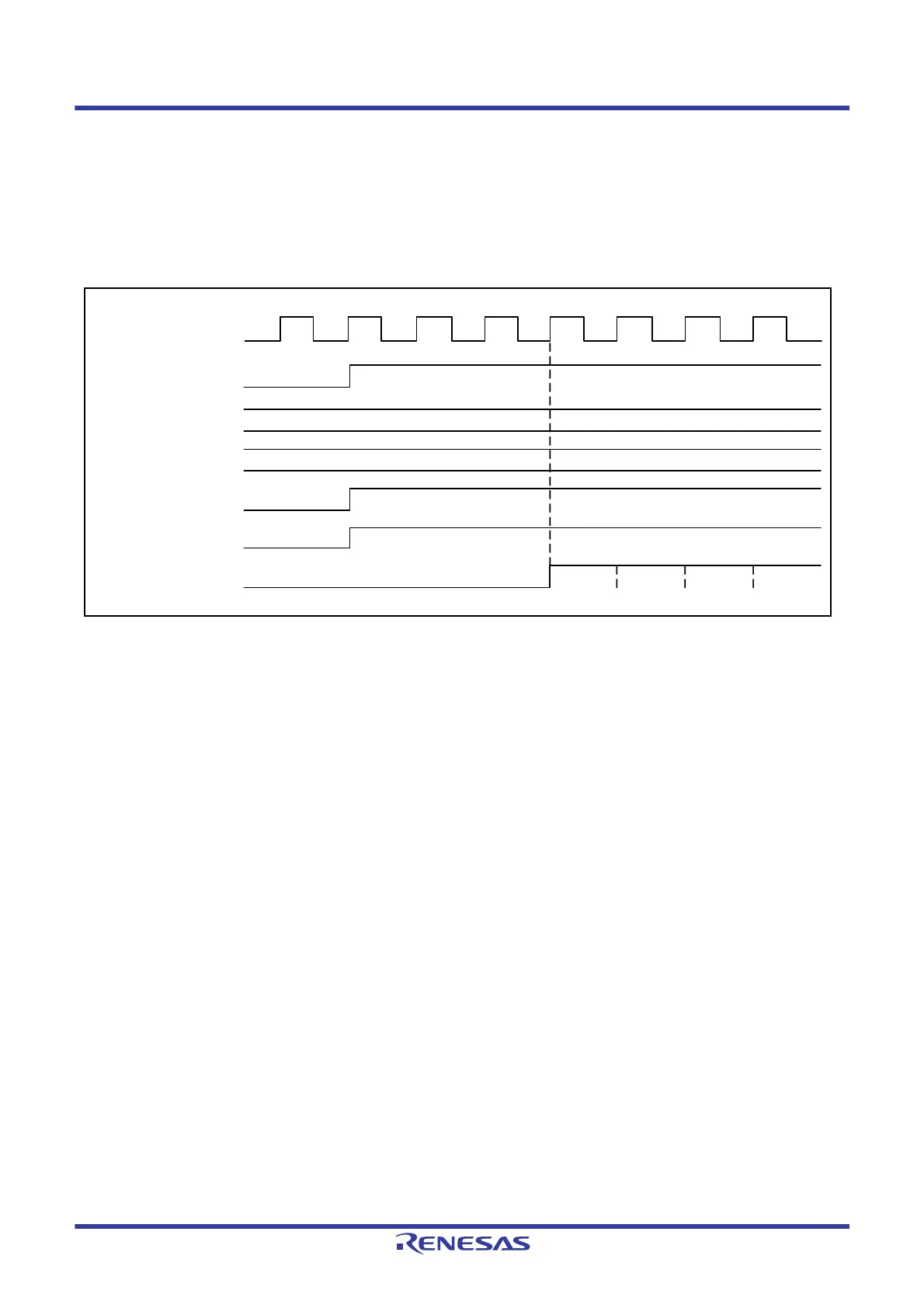

23.6.25 Continuous Output of Interrupt Signal in Response to a Compare Match

When the TGR register is set to 0000h, PCLK/1 is set as the count clock, and compare match is set as the trigger for

clearing of the count clock, the value of the TCNT counter remains 0000h, and the interrupt signal will be output

continuously (i.e. its level will be flat) rather than output over a single cycle. Consequently, interrupts will not be

detected in response to second and subsequent compare matches.

Figure 23.113 shows the timing for continuous output of the interrupt signal in response to a compare match.

Figure 23.113 Continuous Output of Interrupt Signal in Response to a Compare Match

23.6.26 Usage Notes on A/D Converter Delaying Function in Complementary PWM

Mode

When data is transferred from a buffer register at the trough of the MTU4.TCNT counter while the

MTU4.TADCOBRA and MTU4.TADCOBRB registers are set to 0 and the UT4AE and UT4BE bits in the

MTU4.TADCR register are set to 1, no A/D converter start request is issued during up-counting immediately after

transfer. Refer to

Figure 23.114.

When data is transferred from a buffer register at the crest of the MTU4.TCNT counter while the

MTU4.TADCOBRA and MTU4.TADCOBRB registers are set to the same value as the TCDR register and the

UT4AE and UT4BE bits in the MTU4.TADCR register are set to 1, no A/D converter start request is issued during

down-counting immediately after transfer. Refer to

Figure 23.115.

To issue an A/D converter start request linked with interrupt skipping, set the MTU4.TADCORA and

MTU4.TADCORB registers so that 2 ≤ MTU4.TADCORA/TADCORB ≤ TCDR – 2 is satisfied.

PCLK

TSTR.CSTn

TCNT

TGR

Counter clear signal

Compare match signal

Interrupt signal

0000h

0000h

Loading...

Loading...