R01UH0823EJ0100 Rev.1.00 Page 229 of 1823

Jul 31, 2019

RX23W Group 11. Low Power Consumption

11.2.4 Module Stop Control Register C (MSTPCRC)

Note: Set the PRCR.PRC1 bit to 1 (write enabled) before rewriting this register.

Note 1. The MSTPC0 bit should not be set to 1 during access to the RAM. The RAM should not be accessed while the MSTPC0 bit is 1.

Note 2. The MSTPC19 bit should be rewritten while the oscillation of the clock to be controlled by this bit is stable. For entering software

standby mode after rewriting this bit, wait for two cycles of the slowest clock among the clocks output by the oscillators actually

oscillating and execute the WAIT instruction.

DSLPE Bit (Deep Sleep Mode Enable)

The DSLPE bit enables or disables a transition to deep sleep mode.

When the CPU executes the WAIT instruction with the DSLPE bit set to 1 and the SBYCR.SSBY and

MSTPCRA.MSTPA28 bits meet specified conditions, the MCU enters deep sleep mode. For details, refer to

section

11.6.2, Deep Sleep Mode

.

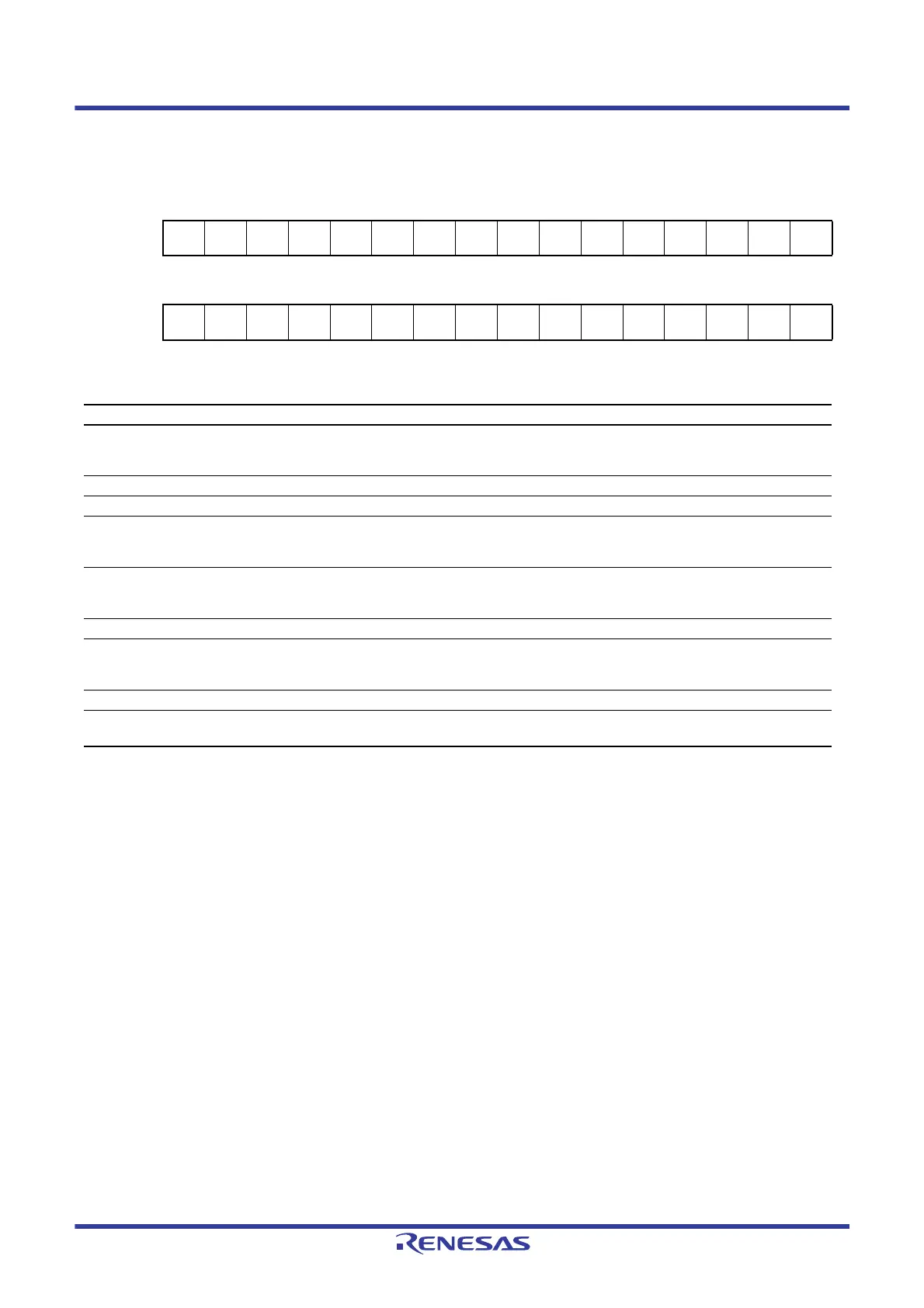

Address(es): 0008 0018h

b31 b30 b29 b28 b27 b26 b25 b24 b23 b22 b21 b20 b19 b18 b17 b16

DSLPE———

MSTPC

27

——————

MSTPC

20

MSTPC

19

———

Value after reset:

0111111111111111

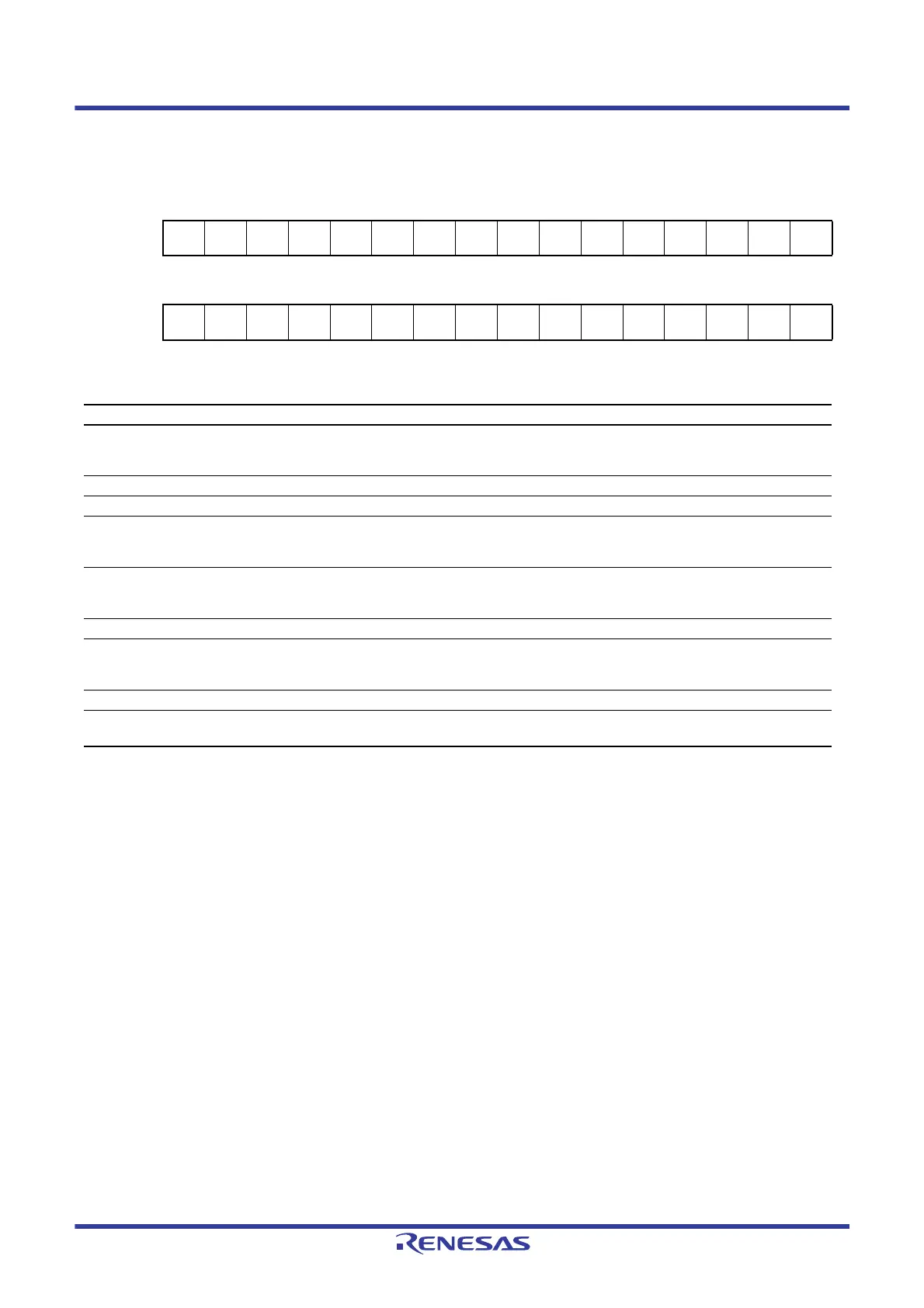

b15 b14 b13 b12 b11 b10 b9 b8 b7 b6 b5 b4 b3 b2 b1 b0

———————————————

MSTPC

0

Value after reset:

0000000000000000

Bit Symbol Bit Name Description R/W

b0 MSTPC0 RAM Module Stop*

1

Target module: RAM (0000 0000h to 0000 FFFFh)

0: RAM operating

1: RAM stopped

R/W

b15 to b1 — Reserved These bits are read as 0. The write value should be 0. R/W

b18 to b16 — Reserved These bits are read as 1. The write value should be 1. R/W

b19 MSTPC19 Clock Frequency Accuracy

Measurement Circuit Module

Stop*

2

Target module: CAC

0: This module clock is enabled

1: This module clock is disabled

R/W

b20 MSTPC20 IrDA Module Stop Target module: IRDA

0: This module clock is enabled

1: This module clock is disabled

R/W

b26 to b21 — Reserved These bits are read as 1. The write value should be 1. R/W

b27 MSTPC27 Serial Communication Interface 8

Module Stop

Target module: SCI8

0: This module clock is enabled

1: This module clock is disabled

R/W

b30 to b28 — Reserved These bits are read as 1. The write value should be 1. R/W

b31 DSLPE Deep Sleep Mode Enable 0: Deep sleep mode is disabled

1: Deep sleep mode is enabled

R/W

Loading...

Loading...