R01UH0823EJ0100 Rev.1.00 Page 357 of 1823

Jul 31, 2019

RX23W Group 18. DMA Controller (DMACA)

18.3 Operation

18.3.1 Transfer Mode

(1) Normal Transfer Mode

In normal transfer mode, one data is transferred by one transfer request. A maximum of 65535 can be set as the number

of transfer operations using the DMCRAL of DMACm. When these bits are set to 0000h, no specific number of transfer

operations is set; data transfer is performed with the transfer counter stopped (free running mode). Setting DMCRB of

DMACm is invalid in normal transfer mode. Except in free running mode, a transfer end interrupt request can be

generated after completion of the specified number of transfer operations.

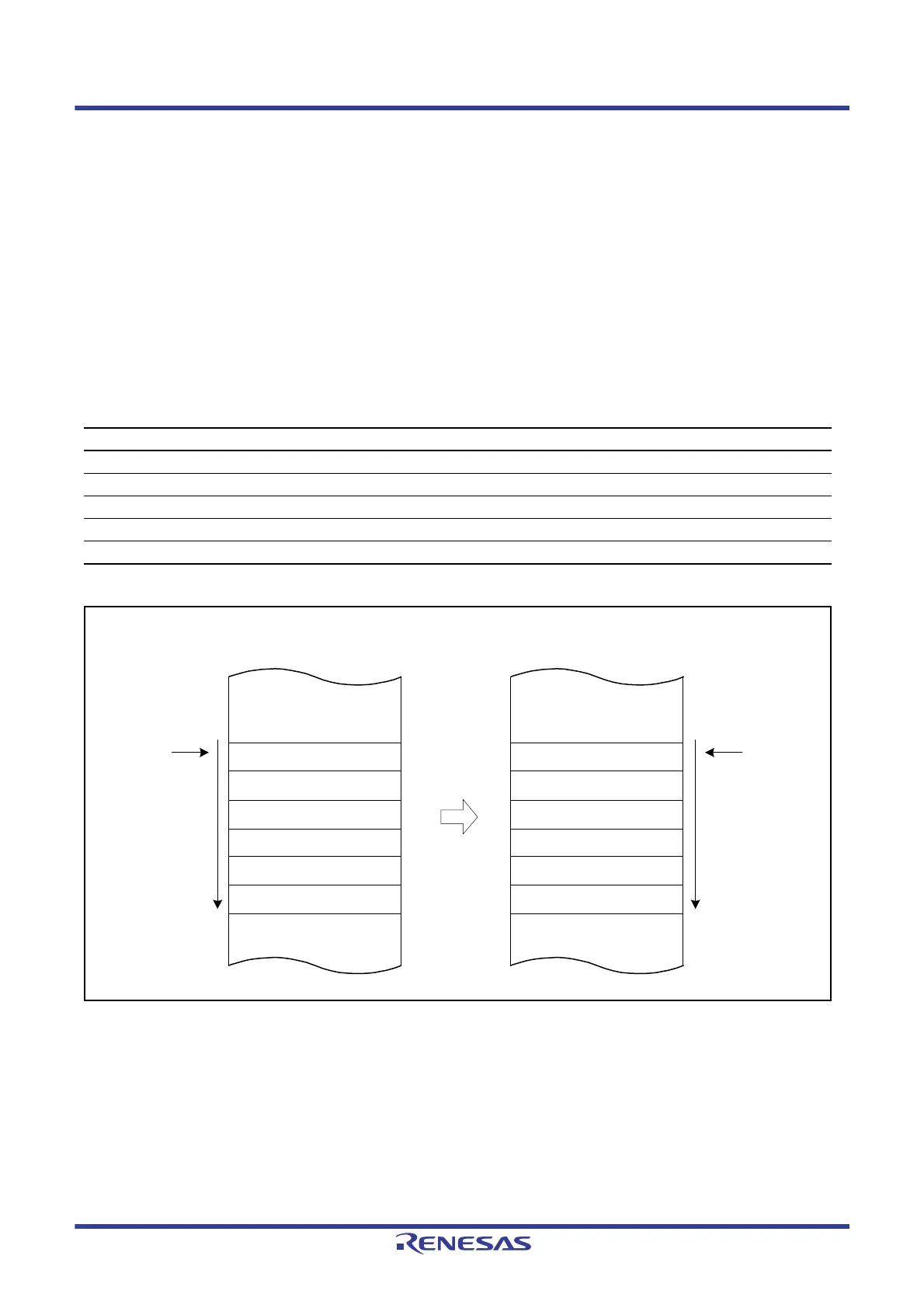

Table 18.3 summarizes the register update operation in normal transfer mode, and Figure 18.2 shows the operation in

normal transfer mode.

Note 1. Offset addition can be specified only for DMAC0.

Figure 18.2 Operation in Normal Transfer Mode

Table 18.3 Register Update Operation in Normal Transfer Mode

Register Function Update Operation after Completion of a Transfer by One Transfer Request

DMACm.DMSAR Transfer source address Increment/decrement/fixed/offset addition*

1

DMACm.DMDAR Transfer destination address Increment/decrement/fixed/offset addition*

1

DMACm.DMCRAL Transfer count Decremented by one/not updated (in free running mode)

DMACm.DMCRAH — Not updated (Not used in normal transfer mode)

DMACm.DMCRB — Not updated (Not used in normal transfer mode)

DMSAR

Transfer source data area

DMDAR

Transfer

Transfer destination data area

Data 1

Data 2

Data 3

Data 4

Data 5

Data 6

Data 1

Data 2

Data 3

Data 4

Data 5

Data 6

Loading...

Loading...