R01UH0823EJ0100 Rev.1.00 Page 723 of 1823

Jul 31, 2019

RX23W Group 25. 16-Bit Timer Pulse Unit (TPUa)

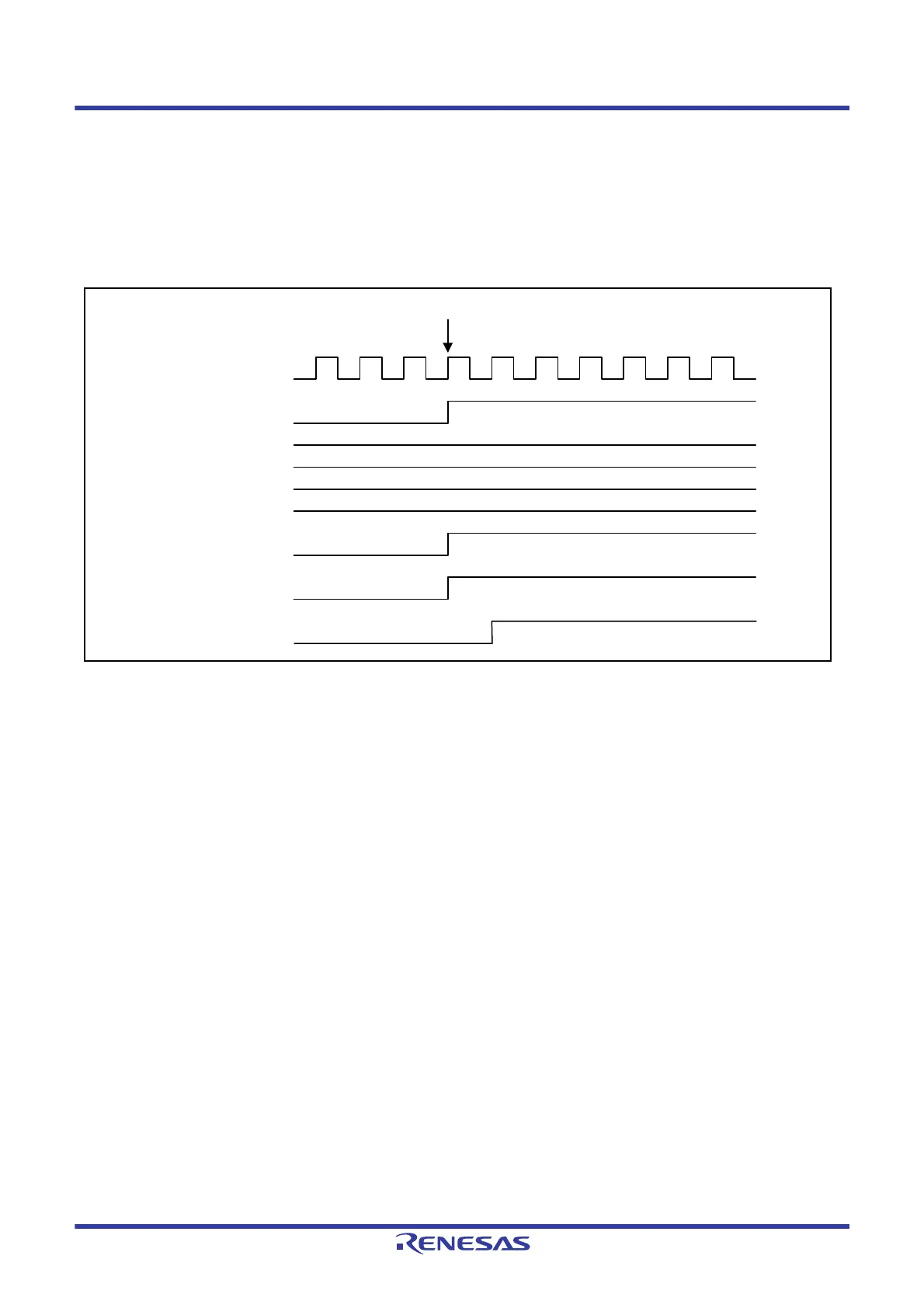

25.9.15 Continuous Output of Compare-Match Pulse Interrupt Signal

When TGR is set to 0000h, PCLK/1 is set as the count clock, and compare match is set as the counter clear source, the

TCNT remains 0000h and is not updated, and a compare-match pulse interrupt signal is output continuously to form a

flat signal level.

When a pulse interrupt signal is used, the interrupt controller cannot detect the second and subsequent interrupts.

Figure 25.53 shows an operation timing when the compare-match pulse interrupt signal is continuously output.

Figure 25.53 Continuous Output of Compare-Match Pulse Interrupt Signal

Write to the timer start register by the CPU

PCLK

TSTR.CST

TCNT

TGR

0000h

0000h

Counter clear signal

Compare match signal

Compare-match pulse

interrupt signal

Loading...

Loading...