R01UH0823EJ0100 Rev.1.00 Page 1570 of 1823

Jul 31, 2019

RX23W Group 44. 12-Bit A/D Converter (S12ADE)

Flush-left format (A/D-converted value addition mode and 1-time to 4-time conversion selected)

Set bits 15 to 2 to the upper-side comparison level for comparison with the A/D-converted value of the same

channel. Write 0 to bits 1 and 0.

Flush-left format (A/D-converted value addition mode and 16-time conversion selected)

Set bits 15 to 0 to the upper-side comparison level for comparison with the A/D-converted value of the same

channel.

When A/D-converted addition mode is selected, set the value added by the A/D-converted value of the same channel.

The number of A/D conversions can be set to 1, 2, 3, 4, or 16 times. If A/D-converted addition mode is selected, when

the A/D conversion count is set to 1 to 4 times, set the number of conversion accuracy bits extended by 2 bits in the

ADCMPDR1 register; when the A/D conversion count is set to 16 times, set the number of conversion accuracy bits

extended by 4 bits in the ADCMPDR1 register.

Even if A/D converted value addition mode is selected, set the reference data in the A/D data register according to the

settings of the A/D data register format select bits.

44.2.27 A/D Compare Function Window A Channel Status Register 0 (ADCMPSR0)

The ADCMPSR0 register stores the comparison results of the compare window A function.

CMPSTCHA0n Flag (n = 00 to 07) (Compare Window A Flag)

This flag is comparison result status flag of channel (AN000 to AN007) to which window A comparison conditions are

applied. When the comparison condition set by ADCMPLR0.CMPLCHAn is met at the end of A/D conversion, each of

these flags is set to 1.

CMPSTCHA000

and

CMPSTCHA007

correspond to AN000 and AN007, respectively.

Writing 1 to the CMPSTCHA0n flag is disabled.

[Setting condition]

The condition set by ADCMPLR0.CMPLCHA0n is met when ADCMPCR.CMPAE = 1

[Clearing condition]

0 is written after reading 1

Address(es): S12AD.ADCMPSR0 0008 90A0h

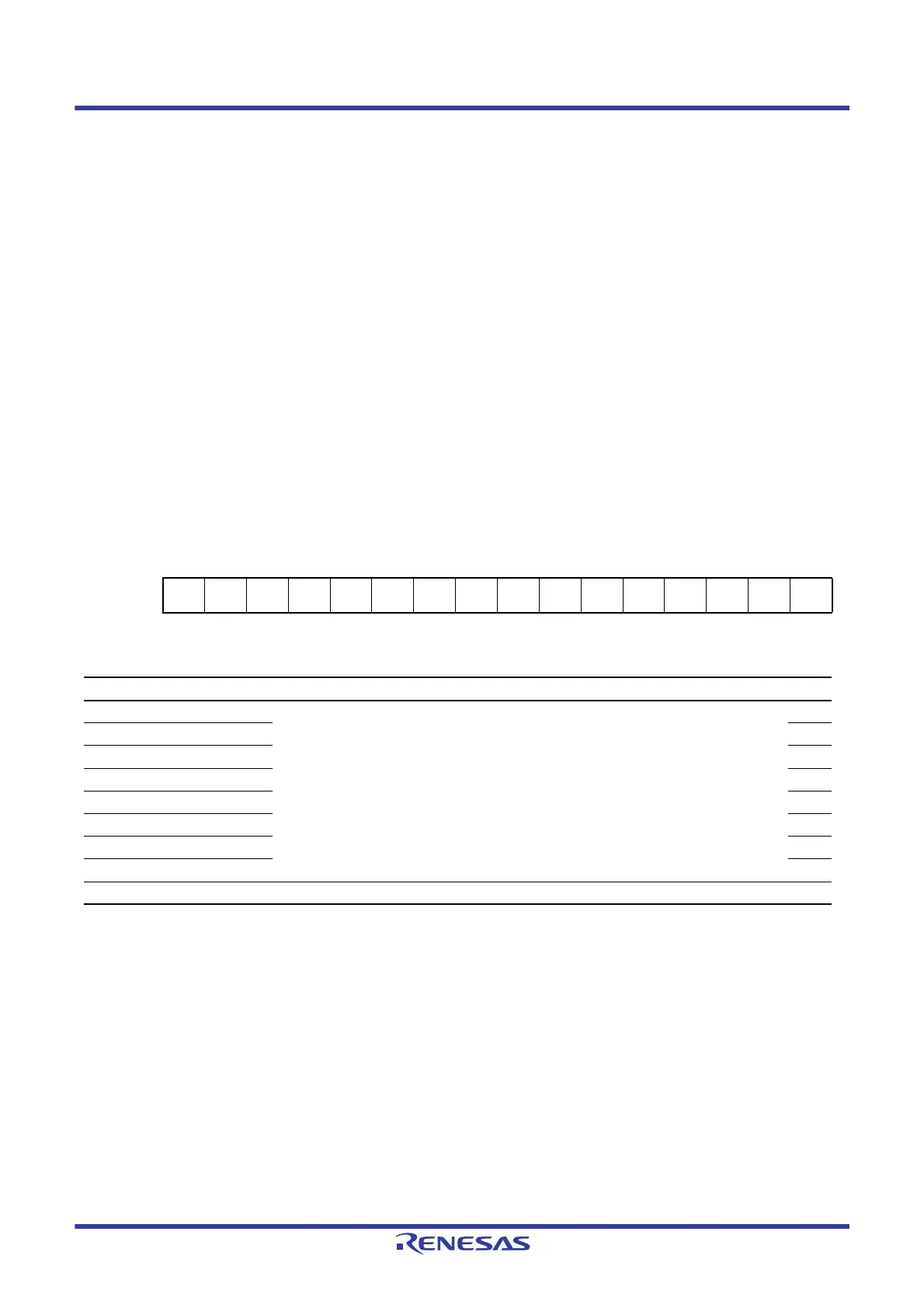

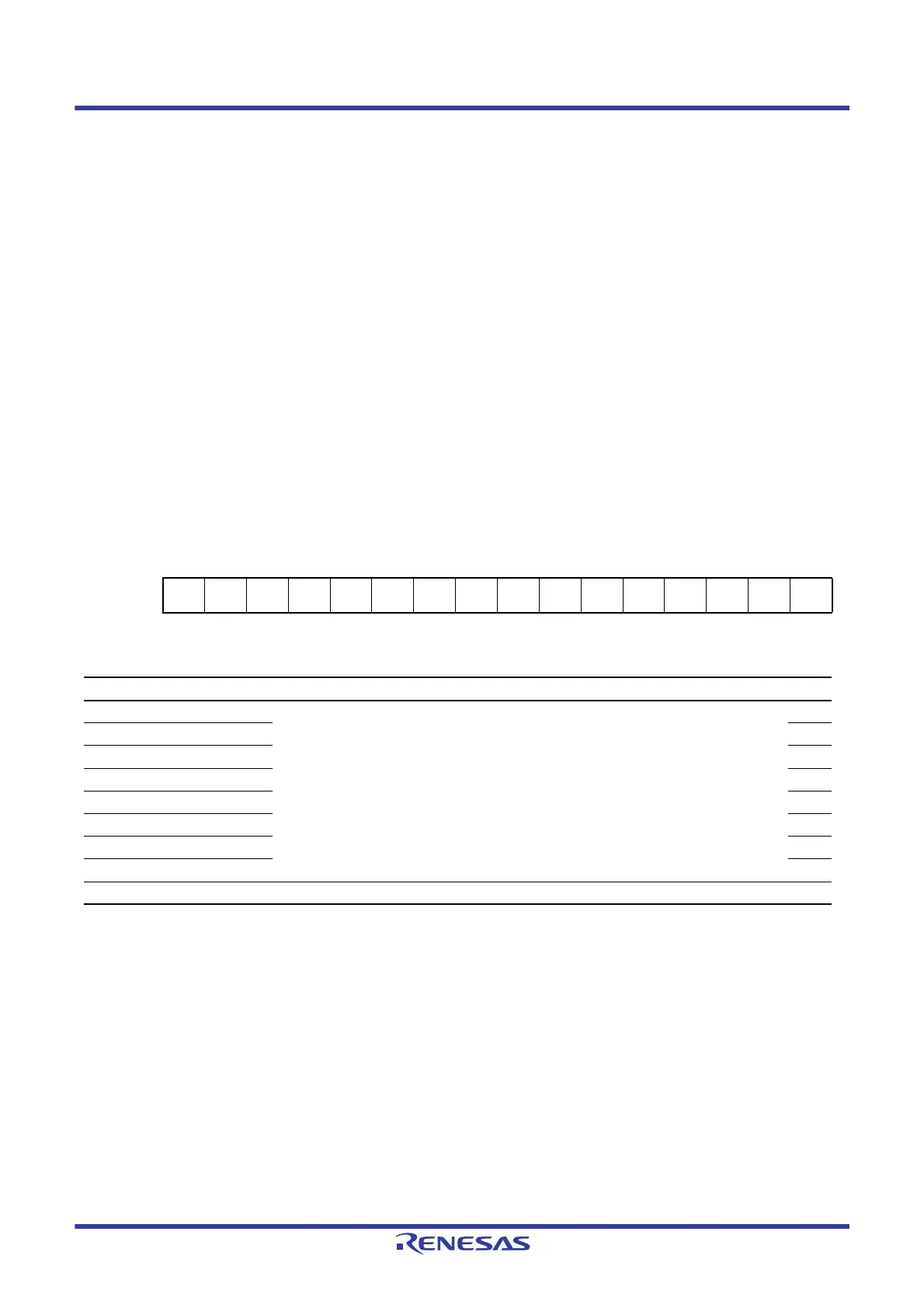

b15 b14 b13 b12 b11 b10 b9 b8 b7 b6 b5 b4 b3 b2 b1 b0

————————

CMPST

CHA007

CMPST

CHA006

CMPST

CHA005

CMPST

CHA004

CMPST

CHA003

CMPST

CHA002

CMPST

CHA001

CMPST

CHA000

Value after reset:

0000000000000000

Bit Symbol Bit Name Description R/W

b0

CMPSTCHA000

Compare Window A Flag When window A operation is enabled (ADCMPCR.CMPAE

= 1), these flags indicate the comparison result of channels

(AN000 to

AN007 to which window A comparison

conditions are applied.

0: Comparison conditions are not met.

1: Comparison conditions are met.

R/W

b1

CMPSTCHA001

R/W

b2

CMPSTCHA002

R/W

b3

CMPSTCHA003

R/W

b4

CMPSTCHA004

R/W

b5

CMPSTCHA005

R/W

b6

CMPSTCHA006

R/W

b7

CMPSTCHA007

R/W

b15 to b8 — Reserved These bits are read as 0. The write value should be 0. R/W

Loading...

Loading...