R01UH0823EJ0100 Rev.1.00 Page 279 of 1823

Jul 31, 2019

RX23W Group 15. Interrupt Controller (ICUb)

15.2.10 IRQ Pin Digital Filter Setting Register 0 (IRQFLTC0)

FCLKSELi[1:0] Bits (IRQi Digital Filter Sampling Clock) (i = 0, 1, and 4 to 7)

These bits select the cycle of the digital filter sampling clock for the IRQi pin.

The sampling clock cycle can be selected from among the PCLK (every cycle), PCLK/8 (once every eight cycles),

PCLK/32 (once every 32 cycles), and PCLK/64 (once every 64 cycles).

For details of the digital filter, see

section 15.4.7, Digital Filter.

Address(es): ICU.IRQFLTC0 0008 7514h

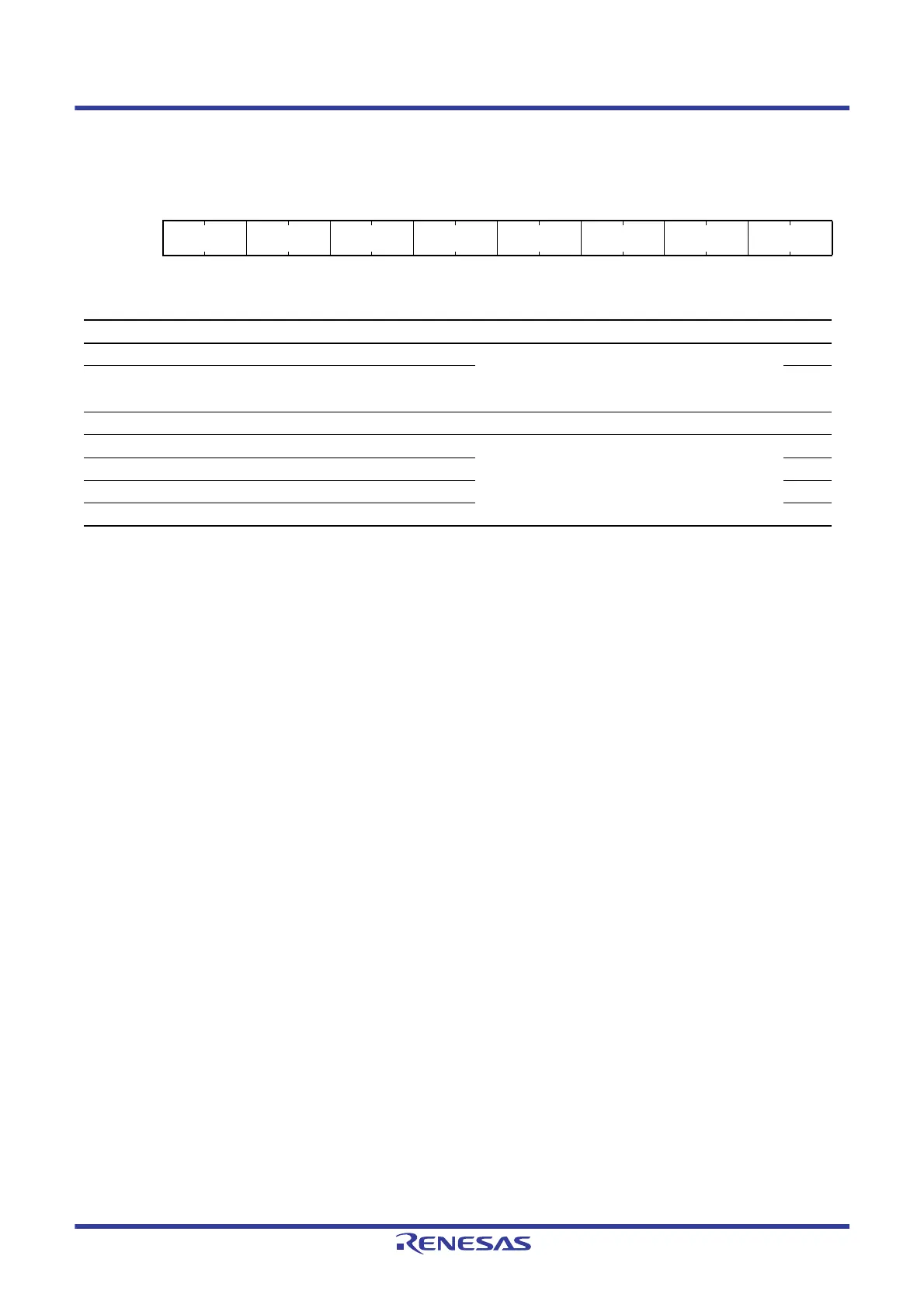

b15 b14 b13 b12 b11 b10 b9 b8 b7 b6 b5 b4 b3 b2 b1 b0

FCLKSEL7[1:0] FCLKSEL6[1:0] FCLKSEL5[1:0] FCLKSEL4[1:0] — — FCLKSEL1[1:0] FCLKSEL0[1:0]

Value after reset:

0000000000000000

Bit Symbol Bit Name Description R/W

b1, b0 FCLKSEL0[1:0] IRQ0 Digital Filter Sampling Clock 0 0: PCLK

0 1: PCLK/8

1 0: PCLK/32

1 1: PCLK/64

R/W

b3, b2 FCLKSEL1[1:0] IRQ1 Digital Filter Sampling Clock R/W

b7 to b4 — Reserved These bits are read as 0. The write value should be 0. R/W

b9, b8 FCLKSEL4[1:0] IRQ4 Digital Filter Sampling Clock 0 0: PCLK

0 1: PCLK/8

1 0: PCLK/32

1 1: PCLK/64

R/W

b11, b10 FCLKSEL5[1:0] IRQ5 Digital Filter Sampling Clock R/W

b13, b12 FCLKSEL6[1:0] IRQ6 Digital Filter Sampling Clock R/W

b15, b14 FCLKSEL7[1:0] IRQ7 Digital Filter Sampling Clock R/W

Loading...

Loading...