R01UH0823EJ0100 Rev.1.00 Page 352 of 1823

Jul 31, 2019

RX23W Group 18. DMA Controller (DMACA)

18.2.10 DMA Software Start Register (DMREQ)

SWREQ Bit (DMA Software Start)

When 1 is written to this bit, a DMA transfer request is generated. After DMA transfer is started in response to the

request, this bit is cleared to 0 if the CLRS bit is set to 0. This bit is not cleared to 0 while the CLRS bit is set to 1. In this

case, a DMA transfer request can be issued again after completion of a transfer.

Note that, however, setting this bit is valid and DMA transfer by software is enabled only when the DCTG[1:0] bits in

DMTMD are set to 00b (DMA activation source is software).

Setting this bit is invalid when the DCTG[1:0] bits in DMTMD are set to a value other than 00b.

To start DMA transfer by software with the CLRS bit being 0, ensure that the SWREQ bit is 0, and then write 1 to the

SWREQ bit.

[Setting condition]

When 1 is written to this bit.

[Clearing conditions]

When a DMA transfer request by software is accepted and DMA transfer is started while the CLRS bit is set to 0

(the SWREQ bit is cleared after DMA transfer is started by software).

When 0 is written to this bit.

CLRS Bit (DMA Software Start Bit Auto Clear Select)

This bit specifies whether to clear the SWREQ bit to 0 after DMA transfer is started in response to the DMA transfer

request generated by setting the SWREQ bit to 1. With this bit set to 0, the SWREQ bit is cleared to 0 after DMA transfer

is started. With this bit set to 1, the SWREQ bit is not cleared to 0. In this case, a DMA transfer request can be issued

again after completion of a transfer.

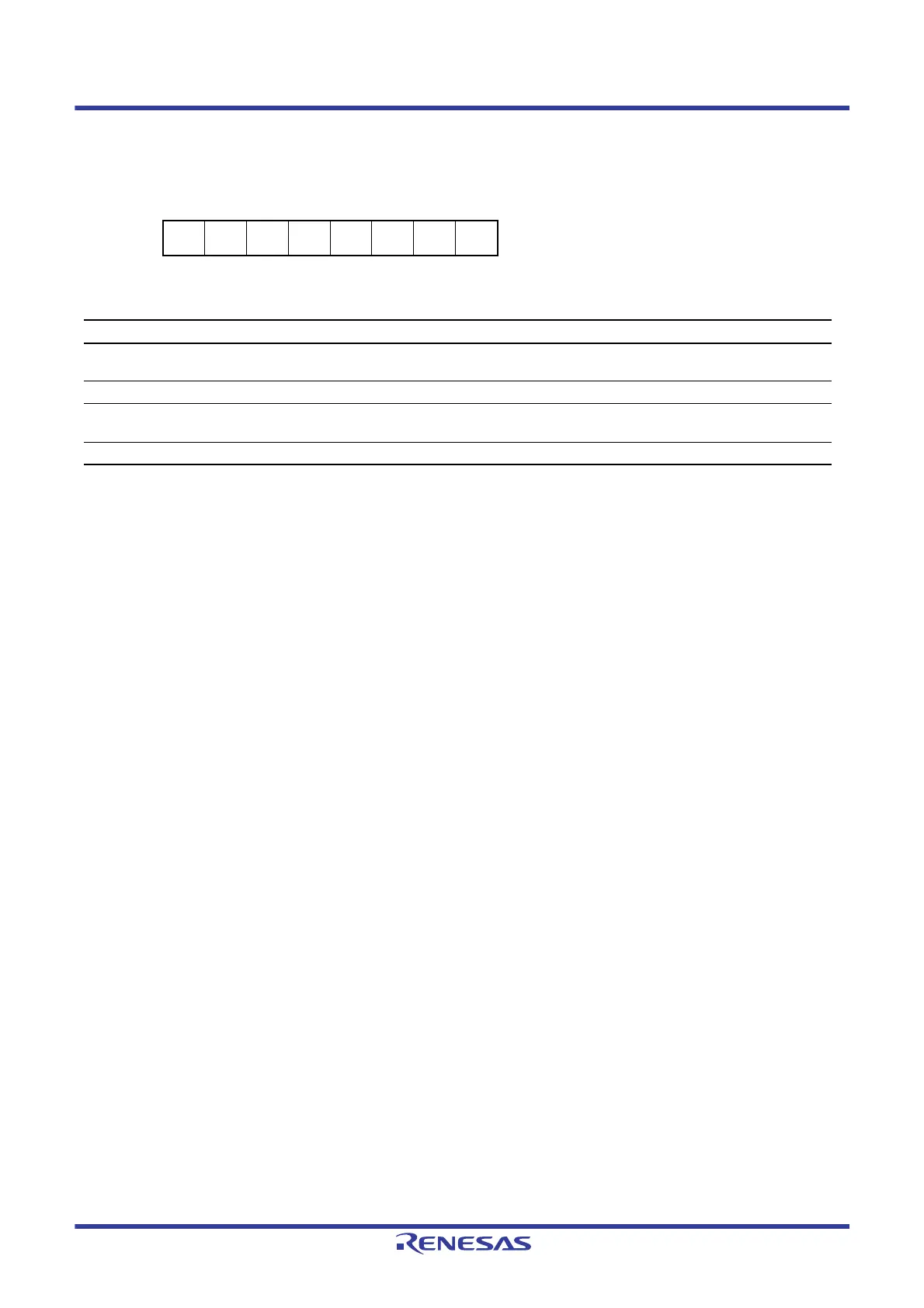

Address(es): DMAC0.DMREQ 0008 201Dh, DMAC1.DMREQ 0008 205Dh, DMAC2.DMREQ 0008 209Dh, DMAC3.DMREQ 0008 20DDh

b7 b6 b5 b4 b3 b2 b1 b0

———CLRS———

SWRE

Q

Value after reset:

00000000

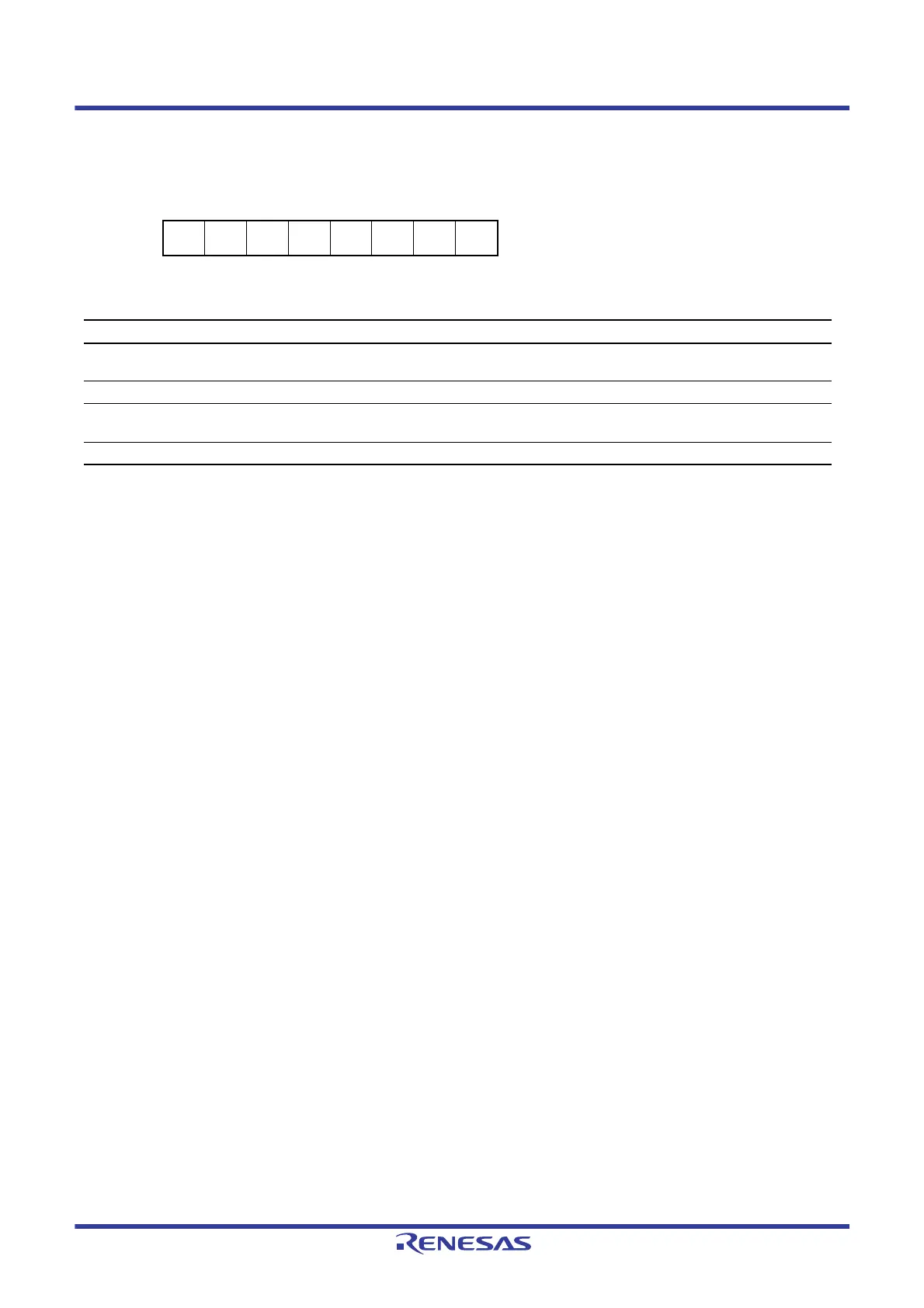

Bit Symbol Bit Name Description R/W

b0 SWREQ DMA Software Start 0: DMA transfer is not requested.

1: DMA transfer is requested.

R/W

b3 to b1 — Reserved These bits are read as 0. The write value should be 0. R/W

b4 CLRS DMA Software Start Bit Auto

Clear Select

0: SWREQ bit is cleared after DMA transfer is started by software.

1: SWREQ bit is not cleared after DMA transfer is started by software.

R/W

b7 to b5 — Reserved These bits are read as 0. The write value should be 0. R/W

Loading...

Loading...