R01UH0823EJ0100 Rev.1.00 Page 811 of 1823

Jul 31, 2019

RX23W Group 29. Low-Power Timer (LPT)

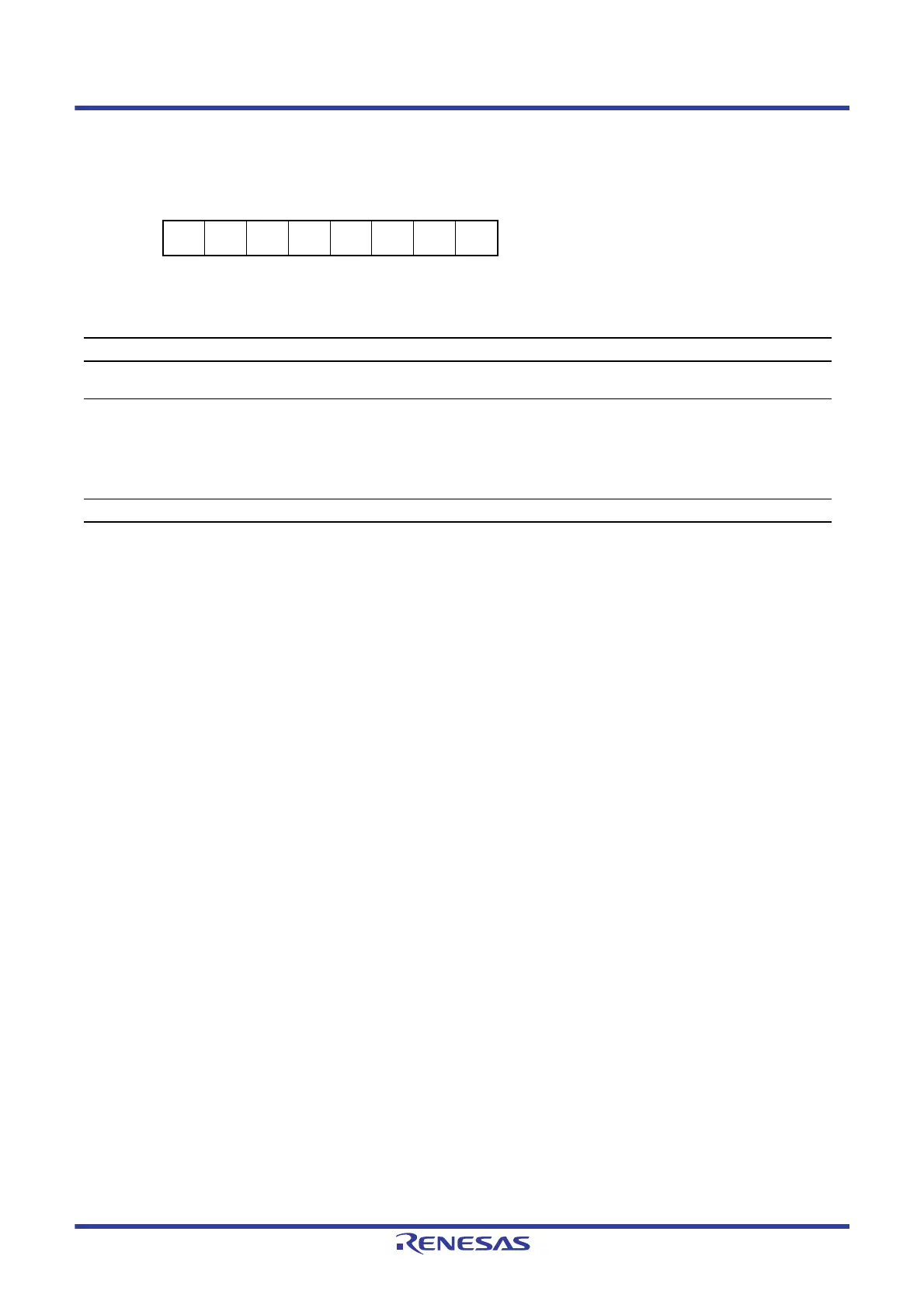

29.2.3 Low-Power Timer Control Register 3 (LPTCR3)

Note: Set the PRCR.PRC2 bit to 1 (write enabled) before rewriting this register.

Note 1. When clearing the low-power timer counter successively, confirm that the LPCNTRST bit becomes 0, wait for at least one cycle

of the clock selected by the LPTCR1.LPCNTCKSEL bit, and then write 1 to the LPCNTRST bit again.

The LPTCR3 register controls operations of and clears the low-power timer counter and divider.

LPCNTEN Bit (Low-Power Timer Counter Operation Control)

This bit is used to operate or stop the low-power timer counter and divider.

When this bit is set to 1 while the LPTCR2.LPCNTSTP bit is 0 (clock is supplied to the low-power timer), the low-

power timer counter and divider start operating. Do not write to this bit while the LPTCR2.LPCNTSTP bit is 1 (supply

of clock to the low-power timer is stopped).

Do not write 1 to the LPCNTRST bit while this bit is 1.

LPCNTRST Bit (Low-Power Timer Counter Clear)

This bit is used to clear the low-power timer counter and divider.

When this bit is set to 1 while the LPTCR2.LPCNTSTP bit is 0 (clock is supplied to the low-power timer), the low-

power timer counter and divider are cleared in synchronization with the clock used for the low-power timer. Once

clearing is complete, this bit automatically becomes 0. Do not write to this bit while the LPTCR2.LPCNTSTP bit is 1

(supply of clock to the low-power timer is stopped).

When 1 is written to this bit, confirm that its value becomes 0 before executing the next processing.

Write to this bit while the LPCNTEN bit is 0 (low-power timer counter stops).

Address(es): LPT.LPTCR3 0008 00B2h

b7 b6 b5 b4 b3 b2 b1 b0

——————

LPCNT

RST

LPCNT

EN

Value after reset:

00000000

Bit Symbol Bit Name Description R/W

b0 LPCNTEN Low-Power Timer Counter

Operation Control

0: Low-power timer counter stops

1: Low-power timer counter operates

R/W

b1 LPCNTRST Low-Power Timer Counter

Clear*

1

When writing

0: Has no effect

1: Clears divider and counter

When reading

0: Clearing is completed

1: Clearing is in progress

R/W

b7 to b2 — Reserved These bits are read as 0. The write value should be 0. R/W

Loading...

Loading...