R01UH0823EJ0100 Rev.1.00 Page 280 of 1823

Jul 31, 2019

RX23W Group 15. Interrupt Controller (ICUb)

15.2.11 Non-Maskable Interrupt Status Register (NMISR)

The NMISR register monitors the status of a non-maskable interrupt source. Writing to the NMISR register is ignored.

The setting in the non-maskable interrupt enable register (NMIER) does not affect the status flags in NMISR.

Before the end of the non-maskable interrupt handler, read the NMISR register and confirm the generation status of other

non-maskable interrupts. Be sure to confirm that all of the bits in the NMISR register are set to 0 before the end of the

handler.

NMIST Flag (NMI Status Flag)

This flag indicates the NMI pin interrupt request.

The NMIST flag is read-only, and cleared by the NMICLR.NMICLR bit.

[Setting condition]

When an edge specified by the NMICR.NMIMD bit is input to the NMI pin

[Clearing condition]

When 1 is written to the NMICLR.NMICLR bit

OSTST Flag (Oscillation Stop Detection Interrupt Status Flag)

This flag indicates the oscillation stop detection interrupt request.

The OSTST flag is read-only, and cleared by the NMICLR.OSTCLR bit.

[Setting condition]

When the oscillation stop detection interrupt is generated

[Clearing condition]

When 1 is written to the NMICLR.OSTCLR bit

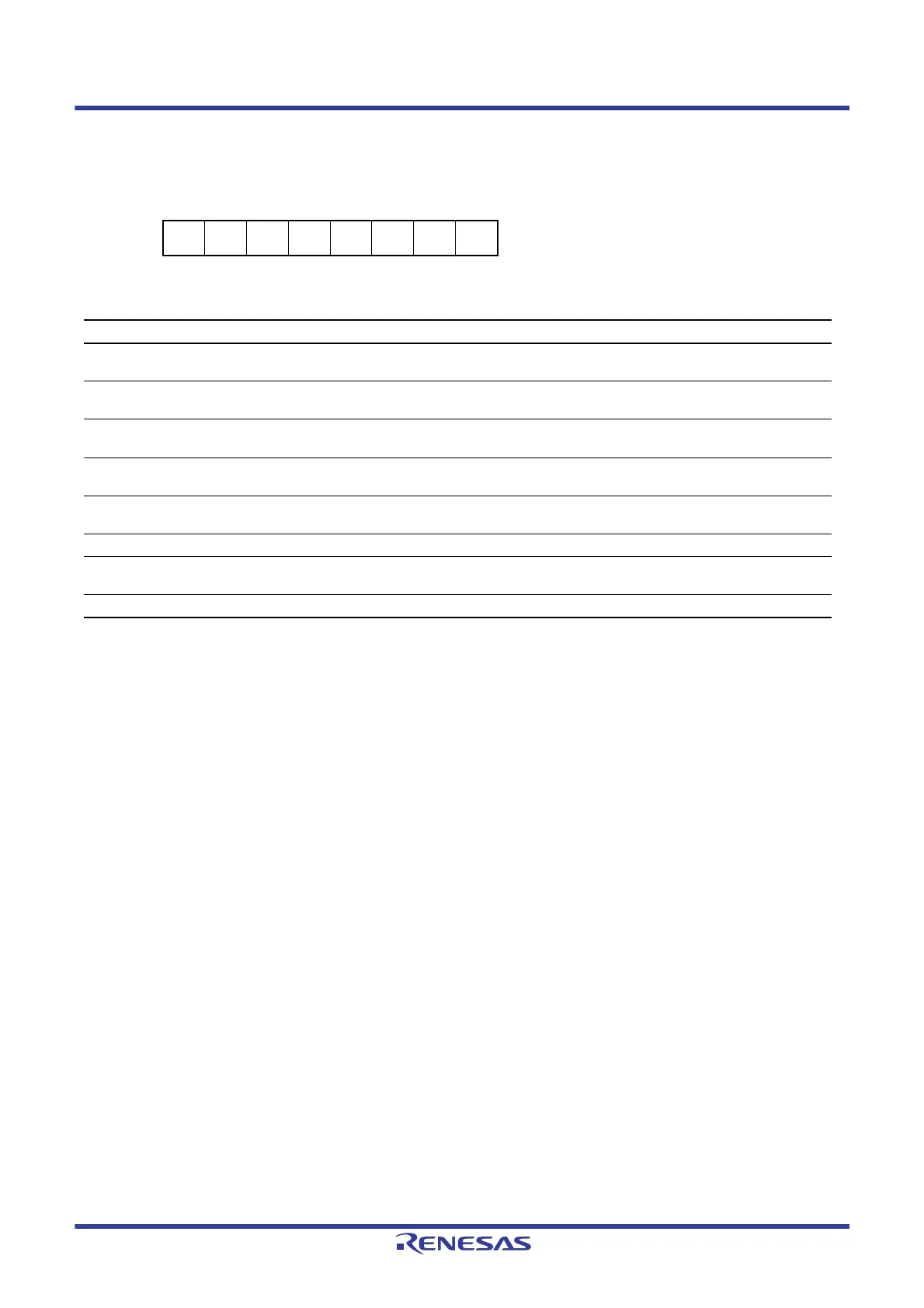

Address(es): ICU.NMISR 0008 7580h

b7 b6 b5 b4 b3 b2 b1 b0

—

VBATS

T

—

LVD1S

T

IWDTS

T

WDTST OSTST NMIST

Value after reset:

00000000

Bit Symbol Bit Name Description R/W

b0 NMIST NMI Status Flag 0: NMI pin interrupt is not requested

1: NMI pin interrupt is requested

R

b1 OSTST Oscillation Stop Detection

Interrupt Status Flag

0: Oscillation stop detection interrupt is not requested

1: Oscillation stop detection interrupt is requested

R

b2 WDTST WDT Underflow/Refresh

Error Status Flag

0: WDT underflow/refresh error interrupt is not requested

1: WDT underflow/refresh error interrupt is requested

R

b3 IWDTST IWDT Underflow/Refresh

Error Status Flag

0: IWDT underflow/refresh error interrupt is not requested

1: IWDT underflow/refresh error interrupt is requested

R

b4 LVD1ST Voltage Monitoring 1

Interrupt Status Flag

0: Voltage monitoring 1 interrupt is not requested

1: Voltage monitoring 1 interrupt is requested

R

b5 — Reserved This bit is read as 0. Writing to this bit has no effect. R

b6 VBATST VBATT Voltage Monitoring

Interrupt Status Flag

0: VBATT voltage monitoring interrupt request is not requested

1: VBATT voltage monitoring interrupt request is requested

R

b7 — Reserved This bit is read as 0. Writing to this bit has no effect. R

Loading...

Loading...