R01UH0823EJ0100 Rev.1.00 Page 402 of 1823

Jul 31, 2019

RX23W Group 19. Data Transfer Controller (DTCa)

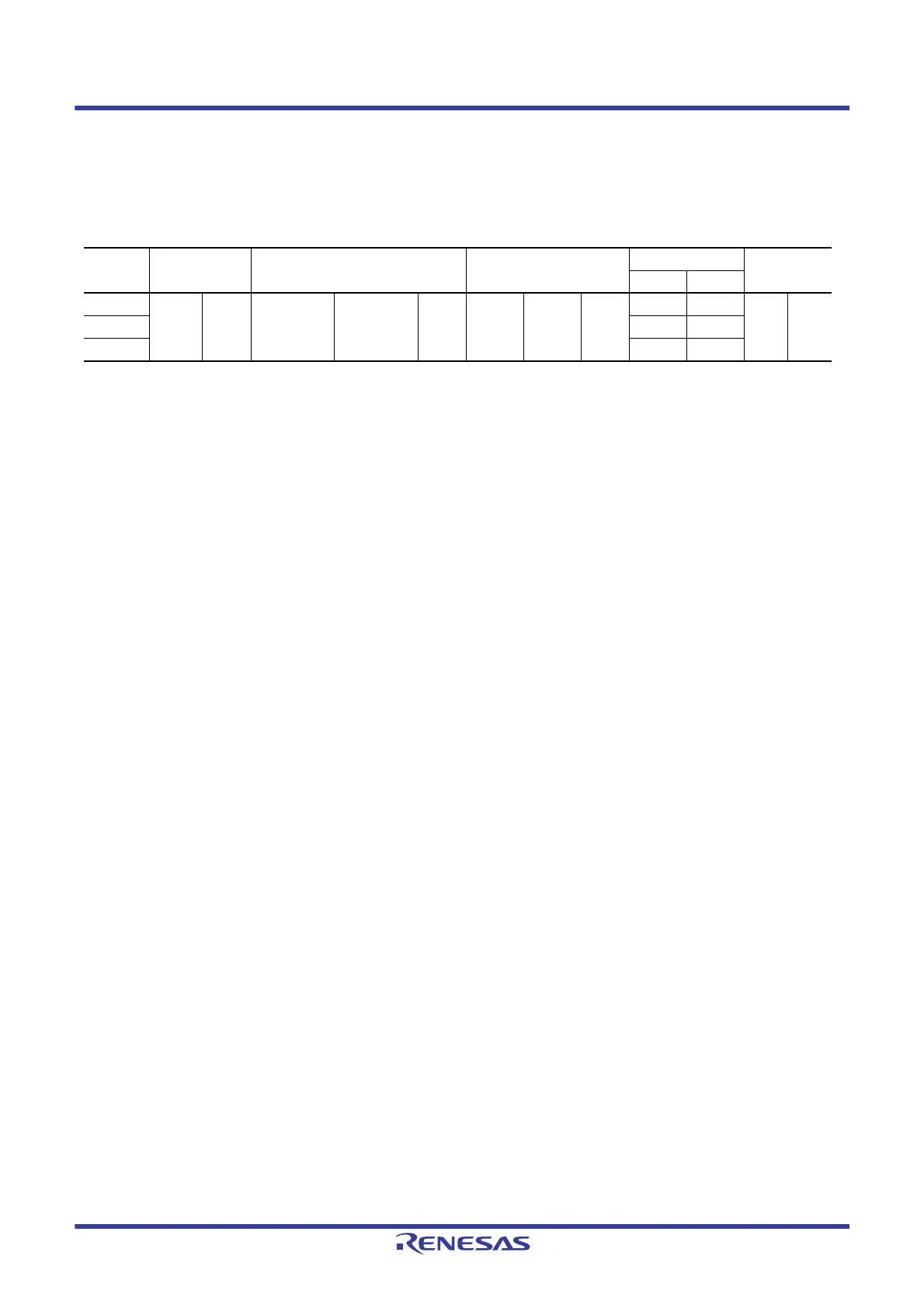

19.4.8 Execution Cycles of the DTC

Table 19.8 lists the execution cycles of single data transfer of the DTC.

For the order of the execution states, refer to

section 19.4.7, Operation Timing.

Note 1. When transfer information read is skipped

Note 2. In full-address mode

Note 3. In short-address mode

Note 4. When neither SAR nor DAR is set to address-fixed

Note 5. When SAR or DAR is set to address-fixed

Note 6. When SAR and DAR are set to address-fixed

Note 7. When the block size is 2 or more. If the block size is 1, the cycle number for normal transfer is applied.

P: Block size (initial settings of CRAH and CRAL)

Cv: Cycles for access to vector transfer information storage destination

Ci: Cycles for access to transfer information storage destination address

Cr: Cycles for access to data read destination

Cw: Cycles for access to data write destination

(The unit is system clocks (ICLK) for “+ 1” in the Vector Read, Transfer Information Read, and Data Transfer Read columns and

“2” in the Internal Operation column.)

(Cv, Ci, Cr, and Cw vary depending on the corresponding access destination. For the number of cycles for respective access

destinations, refer to section 49, RAM, section 50, Flash Memory (FLASH), and section 5, I/O Registers.)

19.4.9 DTC Bus Mastership Release Timing

The DTC does not release the bus mastership during transfer information read and transfer information write. While

transfer information is not read or written, bus arbitration is made according to the priority determined by the bus master

arbitrator.

For bus arbitration, refer to

section 16, Buses.

Table 19.8 Execution Cycles of the DTC

Transfer

Mode Vector Read Transfer Information Read

Transfer Information

Write

Data Transfer

Internal

OperationRead Write

Normal Cv + 1 0*

1

4 × Ci + 1*

2

3 × Ci + 1*

3

0*

1

3 × Ci*

4

2 × Ci*

5

Ci*

6

Cr + 1 Cw 2 0*

1

Repeat Cr + 1 Cw

Block*

7

P × Cr P × Cw

Loading...

Loading...