R01UH0823EJ0100 Rev.1.00 Page 311 of 1823

Jul 31, 2019

RX23W Group 16. Buses

16.3 Register Descriptions

16.3.1 Bus Error Status Clear Register (BERCLR)

Note 1. Only writing 1 is effective; i.e. writing 0 has no effect.

STSCLR Bit (Status Clear)

Writing 1 to this bit clears the bus error status registers 1 and 2 (BERSR1 and BERSR2).

Writing 0 has no effect. It is read as 0.

16.3.2 Bus Error Monitoring Enable Register (BEREN)

Note 1. When detection is disabled (the TOEN bit is cleared to 0), bus access can cause the bus to freeze.

Note 2. Do not clear the TOEN bit to 0 (bus timeout detection disabled) while timeout errors are being detected.

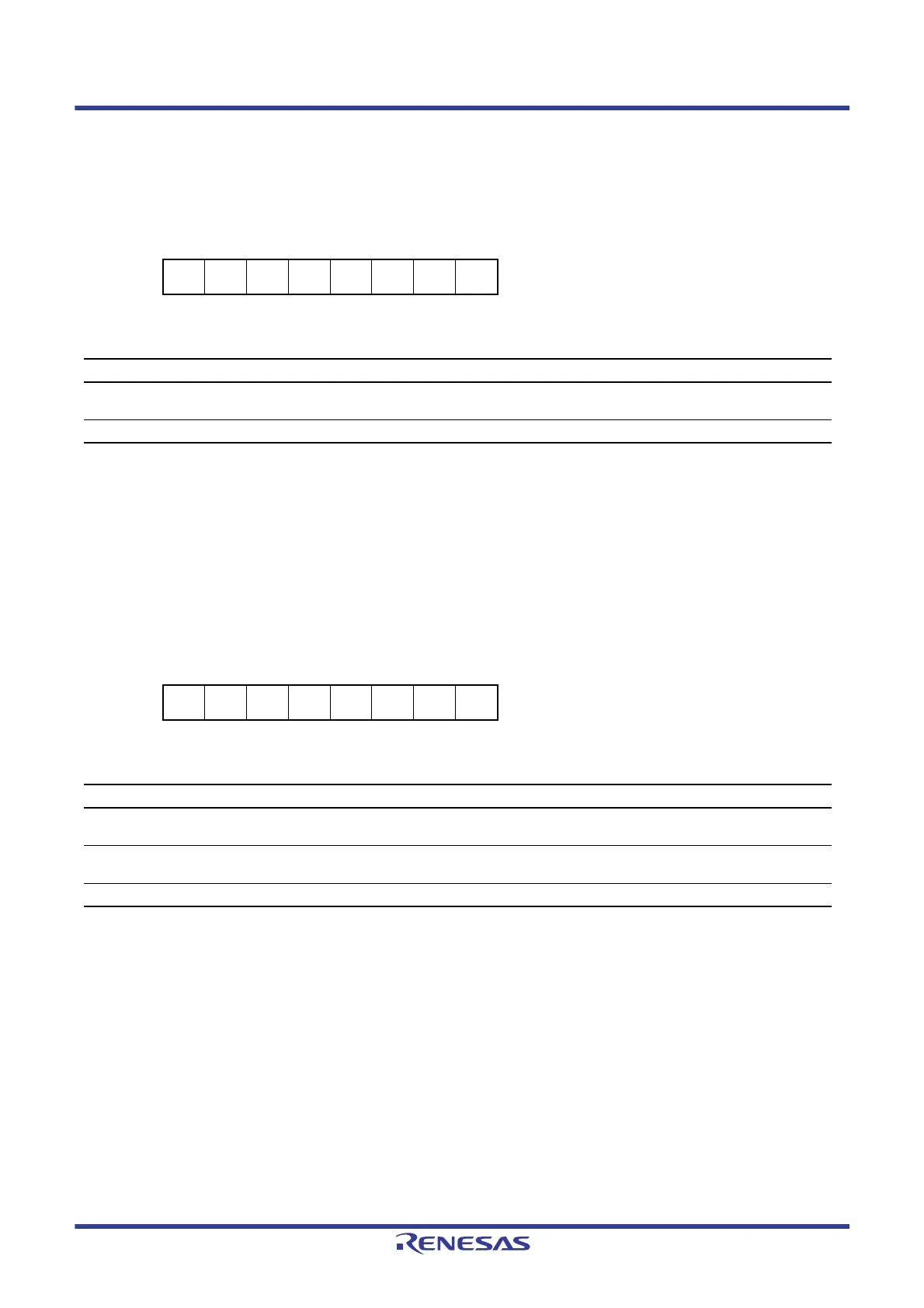

Address(es): 0008 1300h

b7 b6 b5 b4 b3 b2 b1 b0

———————

STSCL

R

Value after reset:

00000000

Bit Symbol Bit Name Description R/W

b0 STSCLR Status Clear 0: Invalid

1: Bus error status register cleared

(W)*

1

b7 to b1 — Reserved These bits are read as 0. The write value should be 0. R/W

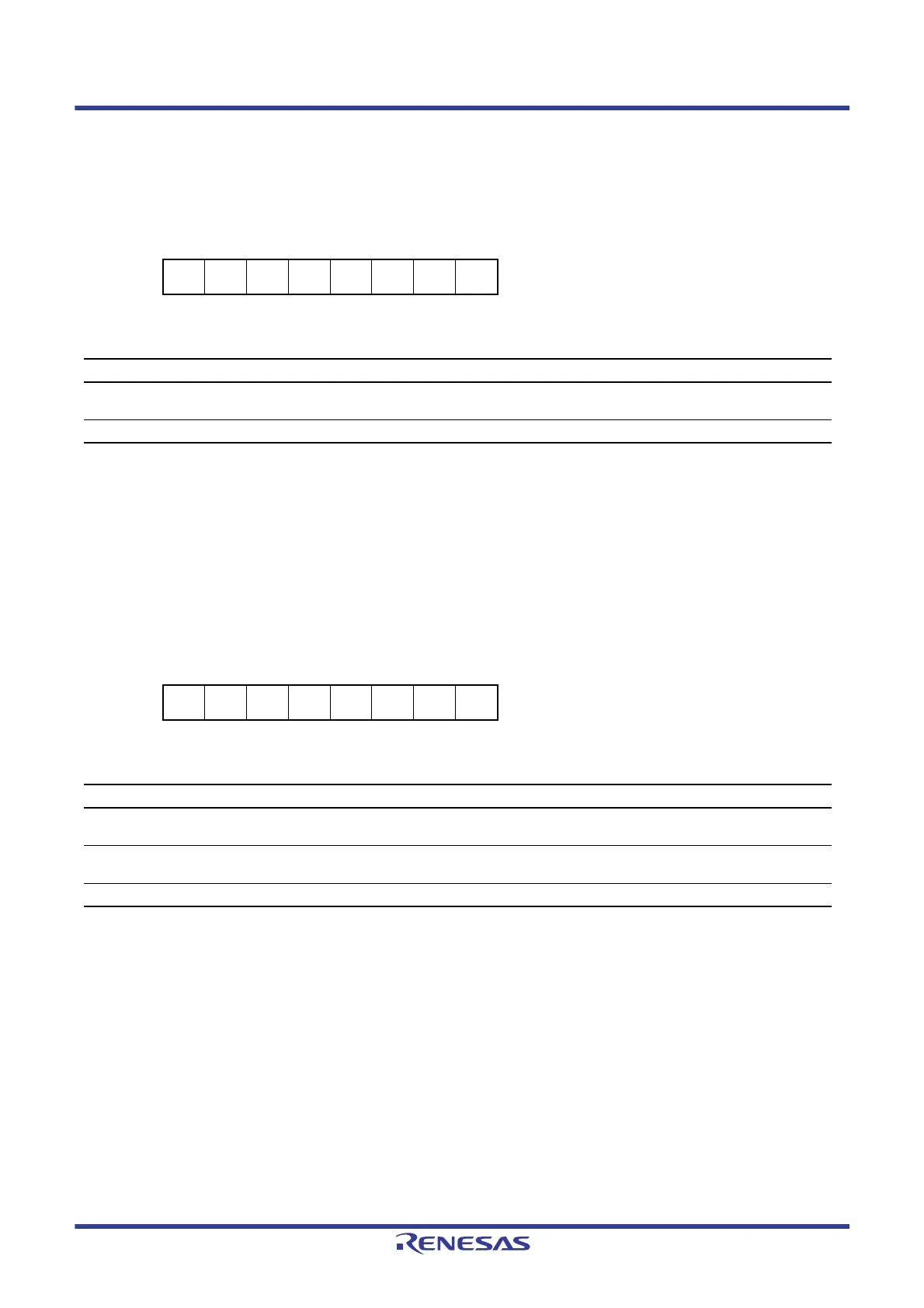

Address(es): 0008 1304h

b7 b6 b5 b4 b3 b2 b1 b0

——————TOENIGAEN

Value after reset:

00000000

Bit Symbol Bit Name Description R/W

b0 IGAEN Illegal Address Access Detection

Enable

0: Illegal address access detection is disabled.

1: Illegal address access detection is enabled.

R/W

b1 TOEN Timeout Detection Enable*

1,

*

2

0: Bus timeout detection is disabled.

1: Bus timeout detection is enabled.

R/W

b7 to b2 — Reserved These bits are read as 0. The write value should be 0. R/W

Loading...

Loading...