R01UH0823EJ0100 Rev.1.00 Page 1420 of 1823

Jul 31, 2019

RX23W Group 40. SD Host Interface (SDHIa)

40. SD Host Interface (SDHIa)

This MCU incorporates an SD host interface (SDHI) which is compliant with the SD Specifications. When developing

host devices that are compliant with the SD Specifications, the user must enter into the SD Host/Ancillary Product

License Agreement (SD HALA).

40.1 Overview

Table 40.1 lists the SDHI specifications.

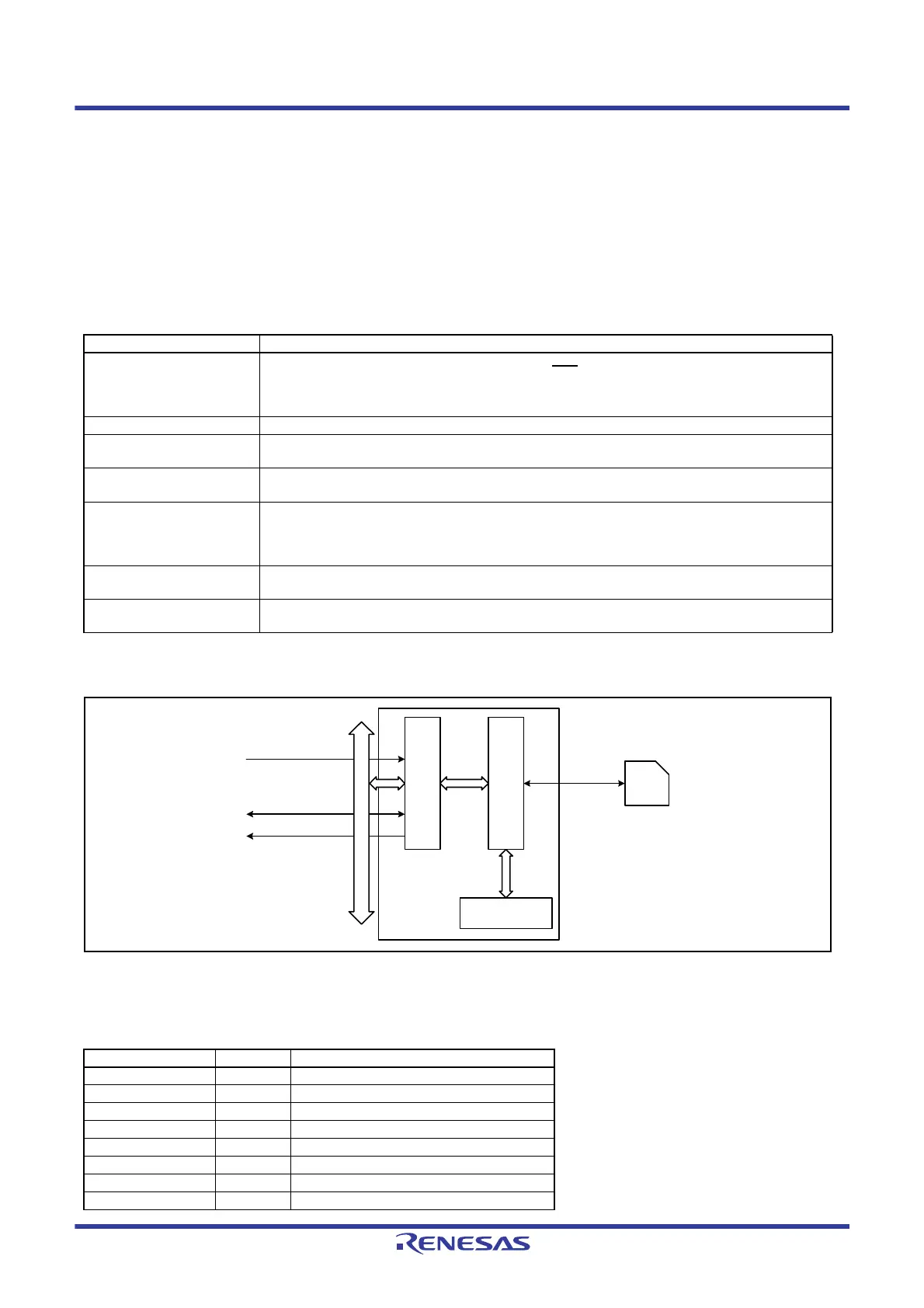

Figure 40.1 shows a block diagram of the SDHI.

Figure 40.1 Block Diagram of the SDHI

Table 40.2 lists the pin configuration of the SDHI.

Table 40.1 SDHI Specifications

Item Description

SD bus interface

Compatible with SD memory card and SDIO card (NOT compatible with the SPI bus interface,

embedded SDIO shared bus, 8-bit SD bus, or SDIO suspend/resume functions)

Transfer bus mode selectable from 4-bit wide bus mode or 1-bit default bus mode

Compatible with SD, SDHC, and SDXC formats

Transfer modes Supports default speed mode

SDHI clock

The SDHI clock is generated by dividing peripheral module clock B (PCLKB) by

n, where n = 1, 2, 4, 8,

16, 32, 64, 128, 256, or 512

Error check functions

CRC7 (command/response)

CRC16 (transfer data)

Interrupt sources

Card access interrupt (CACI)

SDIO access interrupt (SDACI)

Card detection interrupt (CDETI)

SD buffer access interrupt (SBFAI)

DMA transfer sources

DMAC and DTC triggerable by the SBFAI interrupt

SD buffer is read and write accessible using the DMAC and DTC

Other functions

Card detection

Write protection

Table 40.2 Pin Configuration of the SDHI

Pin Name I/O Description

SDHI_CLK Output SDHI clock

SDHI_CMD I/O Command output, response input

SDHI_D0 I/O Data 0 (DAT0)

SDHI_D1 I/O Data 1 (DAT1), SDIO access interrupt

SDHI_D2 I/O Data 2 (DAT2), read wait

SDHI_D3 I/O Data 3 (DAT3), SD card detection

SDHI_CD Input SD card detection

SDHI_WP Input SD card write protection

SD

card

SD card

interface

SD interface

Host interface

SD buffer

(512 bytes × 2)

DMA interface

Interrupt request

PCLKB

Internal peripheral bus

Loading...

Loading...