R01UH0823EJ0100 Rev.1.00 Page 1469 of 1823

Jul 31, 2019

RX23W Group 40. SD Host Interface (SDHIa)

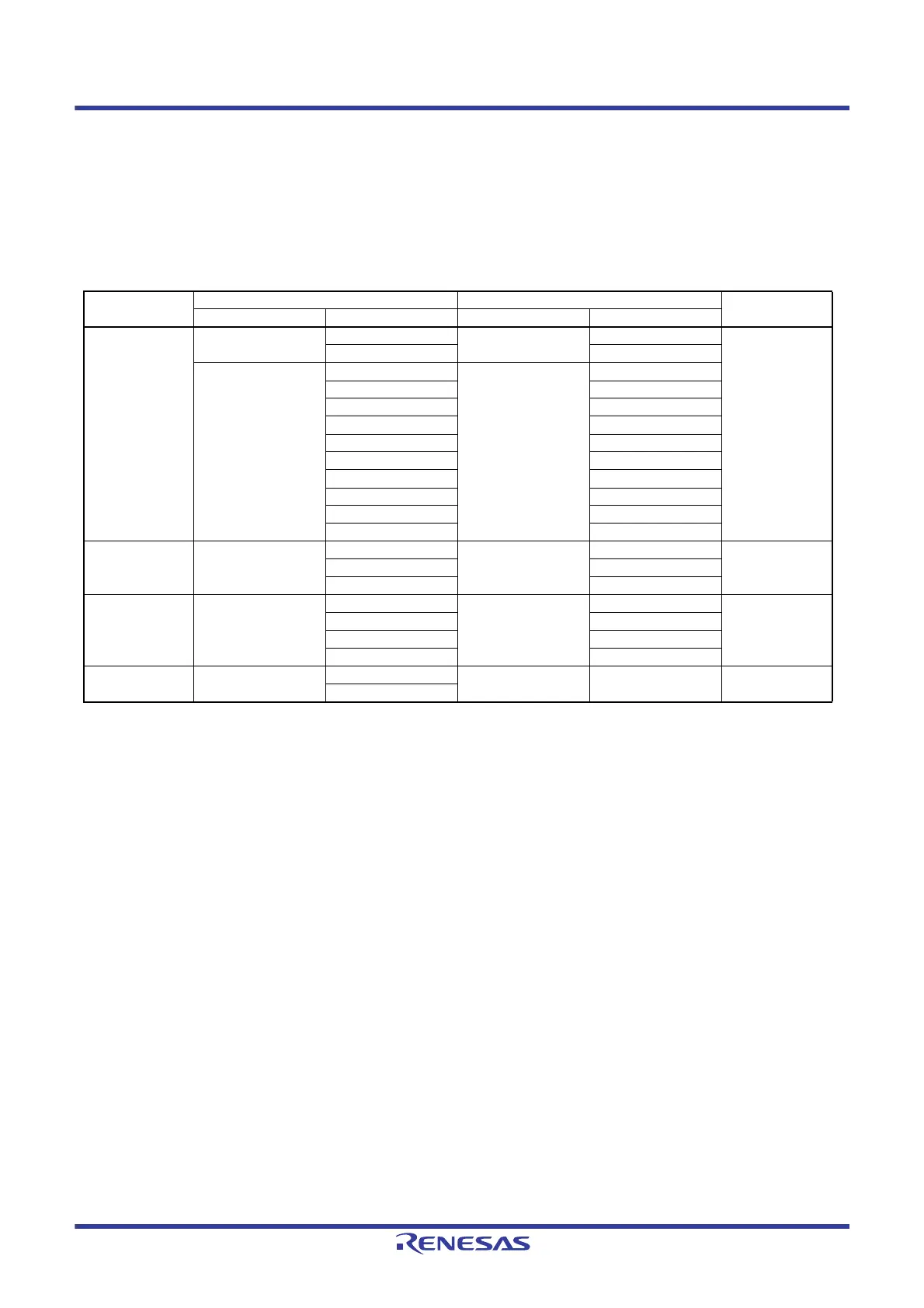

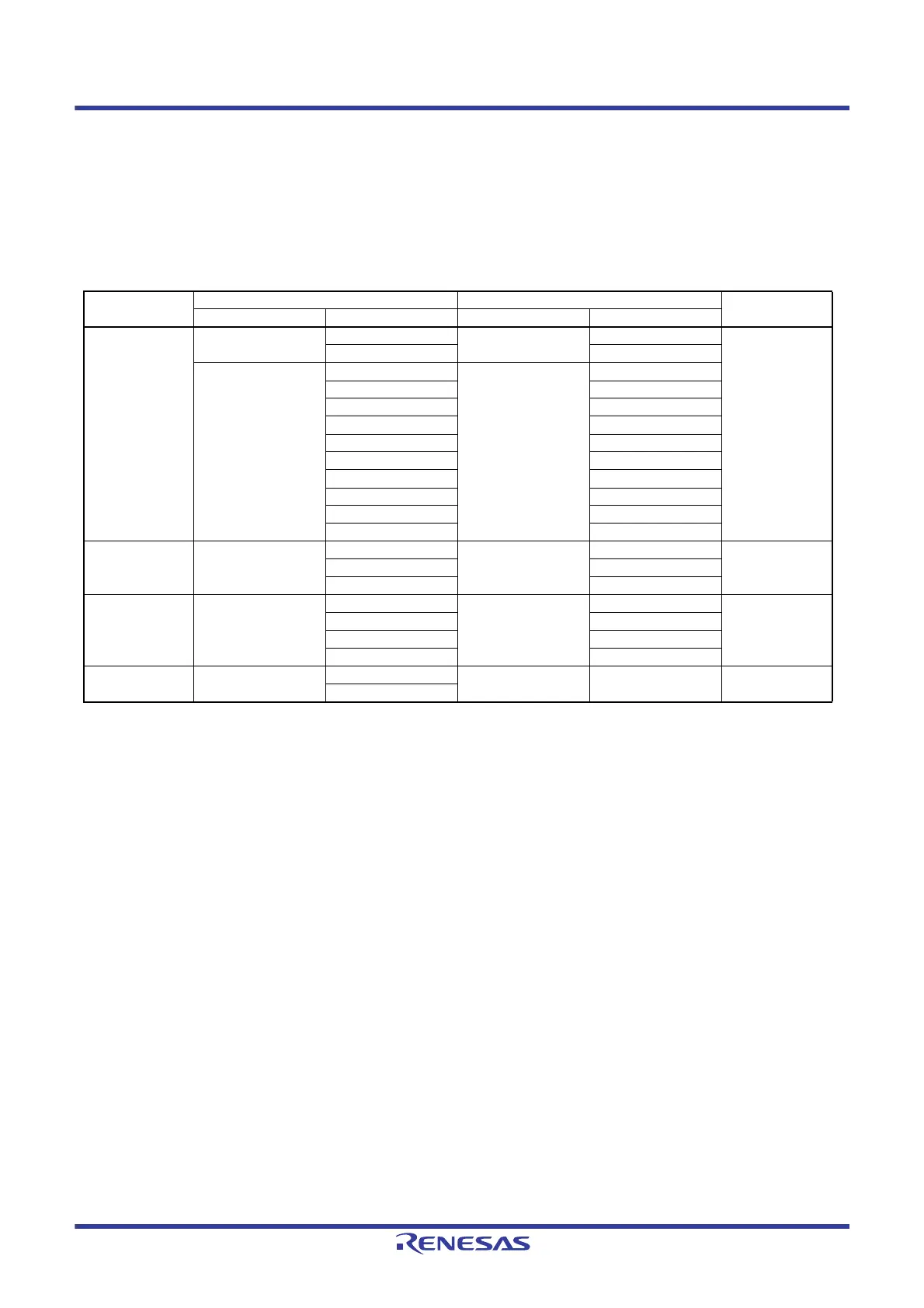

40.4 Interrupts

Table 40.8 lists the SDHI interrupt sources. When the status flags in registers SDSTS1, SDSTS2, and SDIOSTS become

1, if the corresponding bits in registers SDIMSK1, SDIMSK2, and SDIOIMSK are 0, the SDHI requests an interrupt.

When clearing the status flags in registers SDSTS1, SDSTS2, and SDIOSTS, write 0 to the status flags to be cleared and

write 1 to the states flags not being cleared.

Table 40.8 Interrupt Sources

Interrupt Source

Status Flag Register Interrupt Mask/Enable Register

DMAC/DTC

Triggerable

Register symbol Bit symbol Register symbol Bit symbol

CACI

SDSTS1

ACEND

SDIMSK1

ACENDM

No

RSPEND RSPENDM

SDSTS2

ILA

SDIMSK2

ILAM

BWE BWEM

BRE BREM

RSPTO RSPTOM

ILR ILRM

ILW ILWM

DTO DTTOM

ENDE ENDEM

CRCE CRCEM

CMDE CMDEM

SDACI SDIOSTS

EXWT

SDIOIMSK

EXWTM

NoEXPUB52 EXPUB52M

IOIRQ IOIRQM

CDETI SDSTS1

SDD3IN

SDIMSK1

SDD3INM

No

SDD3RM SDD3RMM

SDCDIN SDCDINM

SDCDRM SDCDRMM

SBFAI SDSTS2

BWE

SDDMAEN DMAEN Yes

BRE

Loading...

Loading...