R01UH0823EJ0100 Rev.1.00 Page 83 of 1823

Jul 31, 2019

RX23W Group 2. CPU

2.5 Endian

For the RXv2 CPU, instructions are little endian, but the treatment of data is selectable as little or big endian.

2.5.1 Switching the Endian

As arrangements of bytes, this MCU supports both big endian, where the higher-order byte (MSB) is at location 0, and

little endian, where the lower-order byte (LSB) is at location 0.

For details on the endian setting, see

section 3, Operating Modes.

Operations for access differ according to the endian setting and, depending on the instruction, whether 8-, 16- or 32-bit

access has been selected. Operations for access in the various possible cases are described in

Table 2.1 to Table 2.12.

In the tables,

LL indicates bits D7 to D0 of the general-purpose register,

LH indicates bits D15 to D8 of the general-purpose register,

HL indicates bits D23 to D16 of the general-purpose register, and

HH indicates bits D31 to D24 of the general-purpose register.

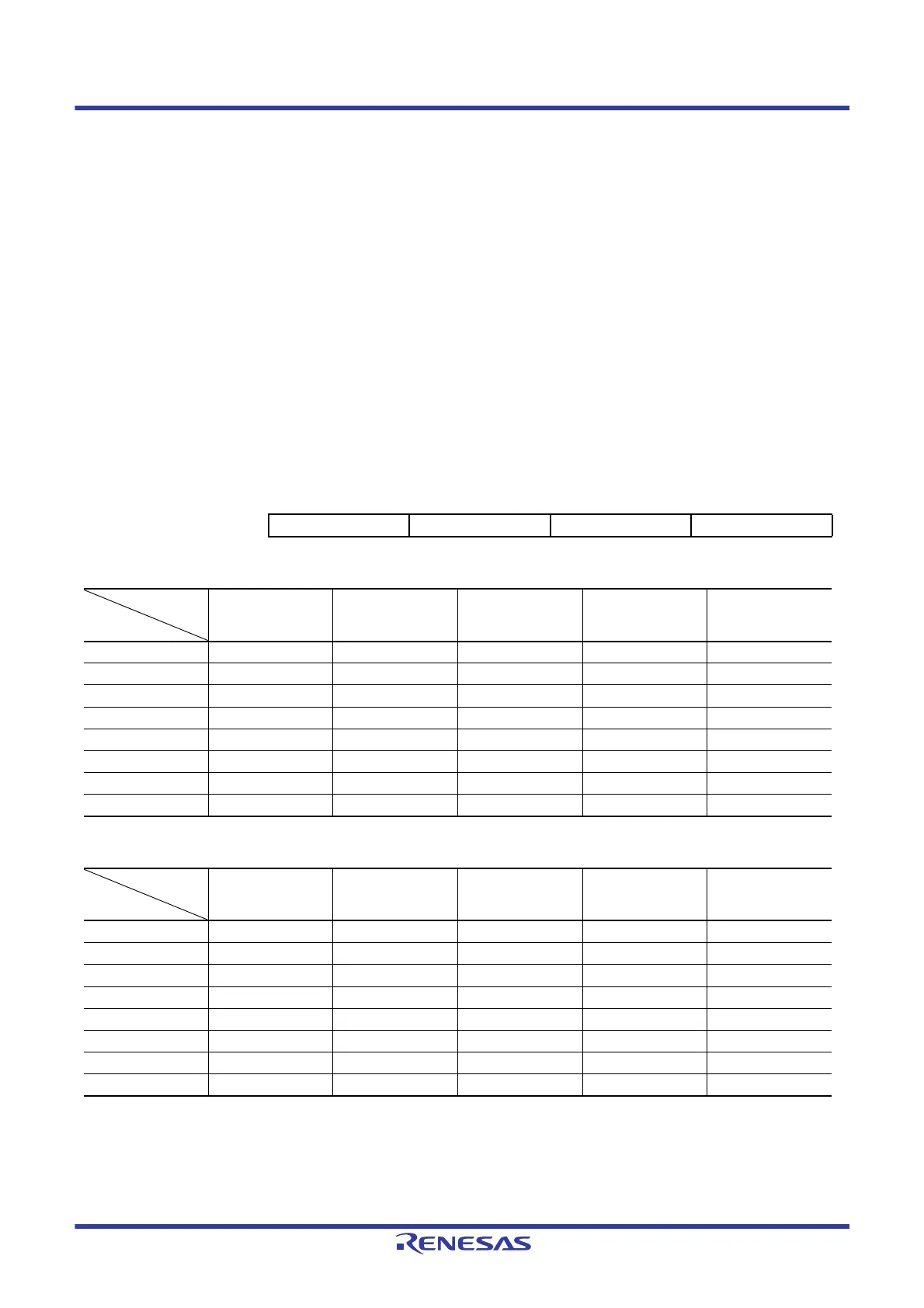

D31 to D24 D23 to D16 D15 to D8 D7 to D0

General purpose register: Rm HH HL LH LL

Table 2.1 32-Bit Read Operations when Little Endian has been Selected

Operation

Address of src

Reading a 32-bit unit

from address 0

Reading a 32-bit unit

from address 1

Reading a 32-bit unit

from address 2

Reading a 32-bit unit

from address 3

Reading a 32-bit unit

from address 4

Address 0 Transfer to LL — — — —

Address 1 Transfer to LH Transfer to LL — — —

Address 2 Transfer to HL Transfer to LH Transfer to LL — —

Address 3 Transfer to HH Transfer to HL Transfer to LH Transfer to LL —

Address 4 — Transfer to HH Transfer to HL Transfer to LH Transfer to LL

Address 5 — — Transfer to HH Transfer to HL Transfer to LH

Address 6 — — — Transfer to HH Transfer to HL

Address 7 — — — — Transfer to HH

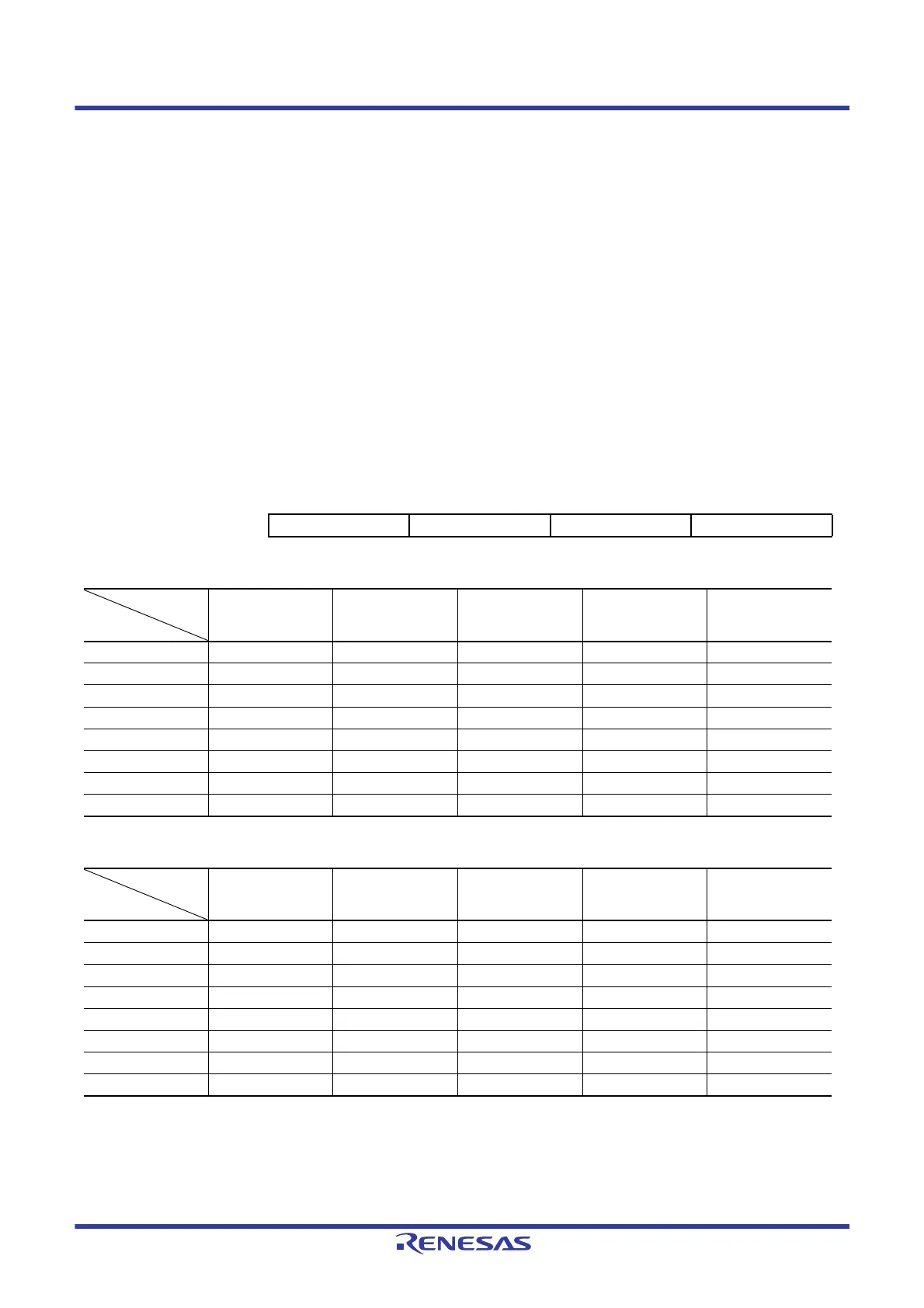

Table 2.2 32-Bit Read Operations when Big Endian has been Selected

Operation

Address of src

Reading a 32-bit unit

from address 0

Reading a 32-bit unit

from address 1

Reading a 32-bit unit

from address 2

Reading a 32-bit unit

from address 3

Reading a 32-bit unit

from address 4

Address 0 Transfer to HH — — — —

Address 1 Transfer to HL Transfer to HH — — —

Address 2 Transfer to LH Transfer to HL Transfer to HH — —

Address 3 Transfer to LL Transfer to LH Transfer to HL Transfer to HH —

Address 4 — Transfer to LL Transfer to LH Transfer to HL Transfer to HH

Address 5 — — Transfer to LL Transfer to LH Transfer to HL

Address 6 — — — Transfer to LL Transfer to LH

Address 7 — — — — Transfer to LL

Loading...

Loading...