R01UH0823EJ0100 Rev.1.00 Page 1451 of 1823

Jul 31, 2019

RX23W Group 40. SD Host Interface (SDHIa)

40.3.5 Communication Errors and Timeouts

When a communication error or timeout error occurs, depending on the type of error, the corresponding status flag in the

SDSTS2 register becomes 1. Also, depending on the source of the error, the corresponding flag in the SDERSTS1 or

SDERSTS2 register becomes 1.

The status flags in registers SDERSTS1 and SDERSTS2 become 0 by writing to the SDCMD register, or by setting the

SDRST.SDRST bit to 0.

Note 1. CMD12 or CMD52 which are automatically issued to stop transfer.

Note 2. A command other than CMD12 or CMD52 which are automatically issued to stop transfer.

Note 1. CMD12 or CMD52 which are automatically issued to stop transfer.

Note 2. A command other than CMD12 or CMD52 which are automatically issued to stop transfer.

Note 3. The period is set in the SDOPT.TOP[3:0] bits.

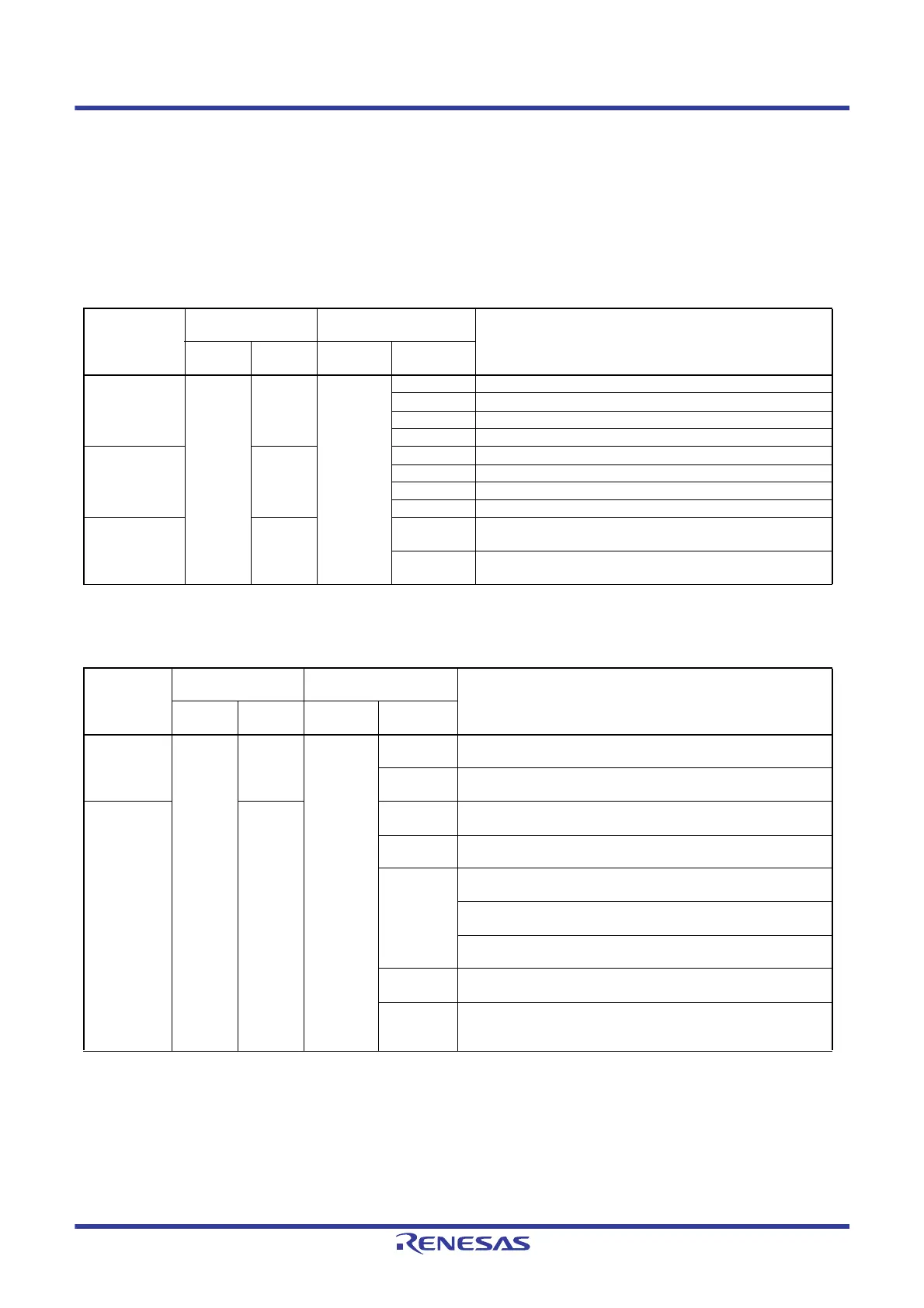

Table 40.6 Communication Errors

Communication

Error

Interrupt Flag

Register

Error Status Register

This Occurs When...

Register

symbol

Bit

symbol

Register

symbol

Bit symbol

End bit error

SDSTS2

ENDE

SDERSTS1

CRCLENE The CRC status token length is in error

RDLENE The read data length is in error

RSPLENE1 The response length is in error

*1

RSPLENE0 The response length is in error

*2

CRC error CRCE

CRCTKE The CRC status token is in error

RDCRCE There is a CRC error in the read data

RSPCRCE1 There is a CRC error in the response

*1

RSPCRCE0 There is a CRC error in the response

*2

Command error CMDE

CMDE1

The command index field value for the transmitted command

and received response do not match

*1

CMDE0

The command index field value for the transmitted command

and received response do not match

*2

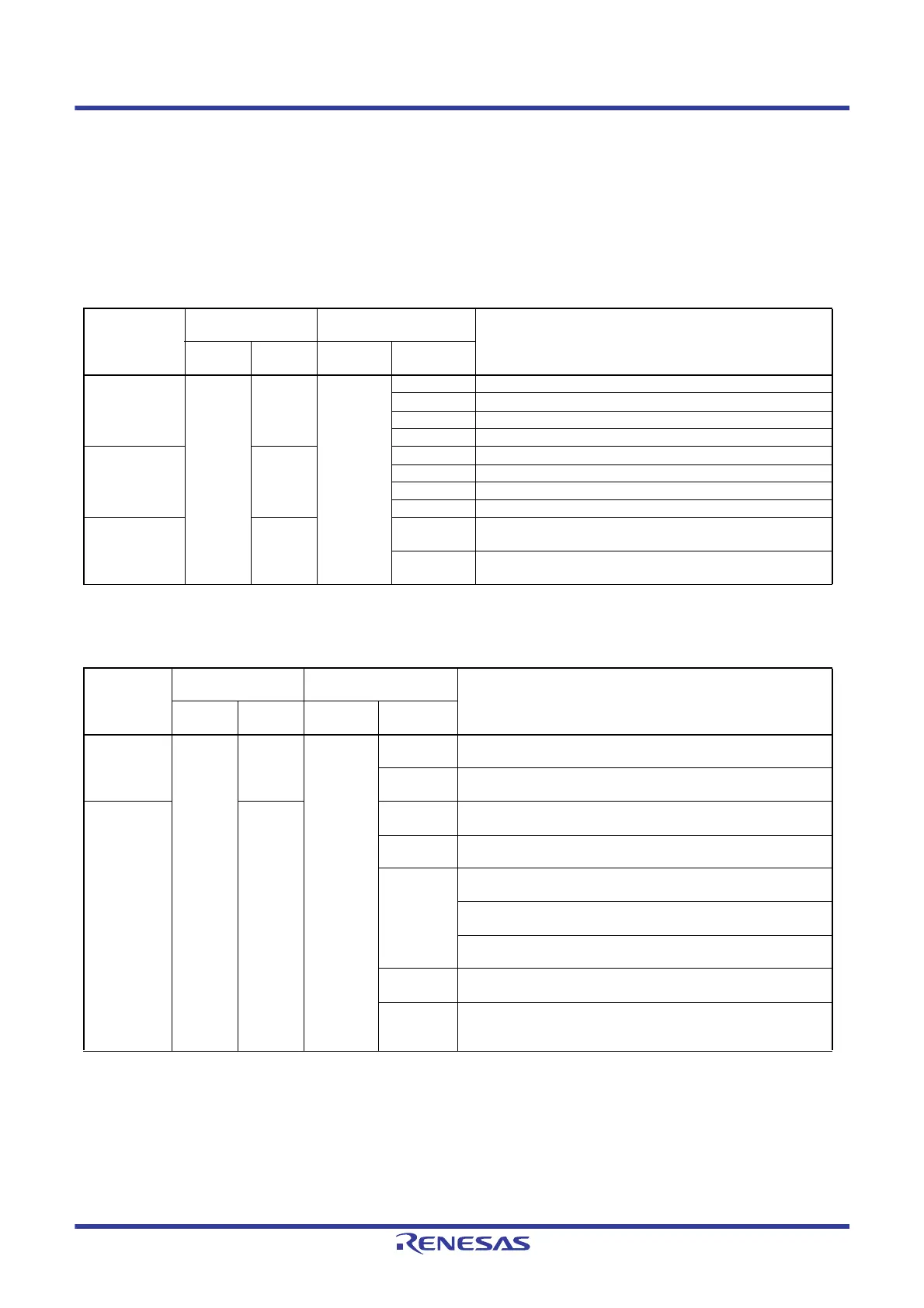

Table 40.7 Timeouts

Timeout

Interrupt Flag

Register

Error Status Register

This Occurs When...

Register

symbol

Bit

symbol

Register

symbol

Bit symbol

Response

timeout

SDSTS2

RSPTO

SDERSTS2

RSPTO1

A response is not received even after a minimum of 640 SDHI clock

cycles elapse

*1

RSPTO0

A response is not received even after a minimum of 640 SDHI clock

cycles elapse

*2

Data timeout

(excluding

response

timeout)

DTO

CRCBSYTO

After the CRC status token is received, the SDHI is busy for at least

the period set

*3

CRCTO

After the write data is transmitted, the CRC status token is not

received even after at least the period set

*3

elapses

RDTO

After the read command is issued, the read data is not received

even after at least the period set

*3

elapses

After the read data is received, the next block read data is not

received even after at least the period set

*3

elapses

After the SDHI exits the read wait state, the next block read data is

not received even after at least the period set

*3

elapses

BSYTO1

After CMD12 is issued during the command sequence, the SDHI is

busy for at least the period set

*3

BSYTO0

After the R1b response is received, the SDHI is busy for at least the

period set

*3

(a command other than CMD12 is issued during the

command sequence)

Loading...

Loading...