R01UH0823EJ0100 Rev.1.00 Page 820 of 1823

Jul 31, 2019

RX23W Group 30. Watchdog Timer (WDTA)

30. Watchdog Timer (WDTA)

The watchdog timer (WDT) is a 14-bit down-counter. It can be used to reset this MCU when the counter underflows

because its value cannot be refreshed due to the system being out of control.

In addition, a non-maskable interrupt can be generated by an underflow.

The refresh-permitted period can be set to refresh the counter and used as the condition to detect when the system runs

out of control.

In this section, “PCLK” is used to refer to PCLKB.

30.1 Overview

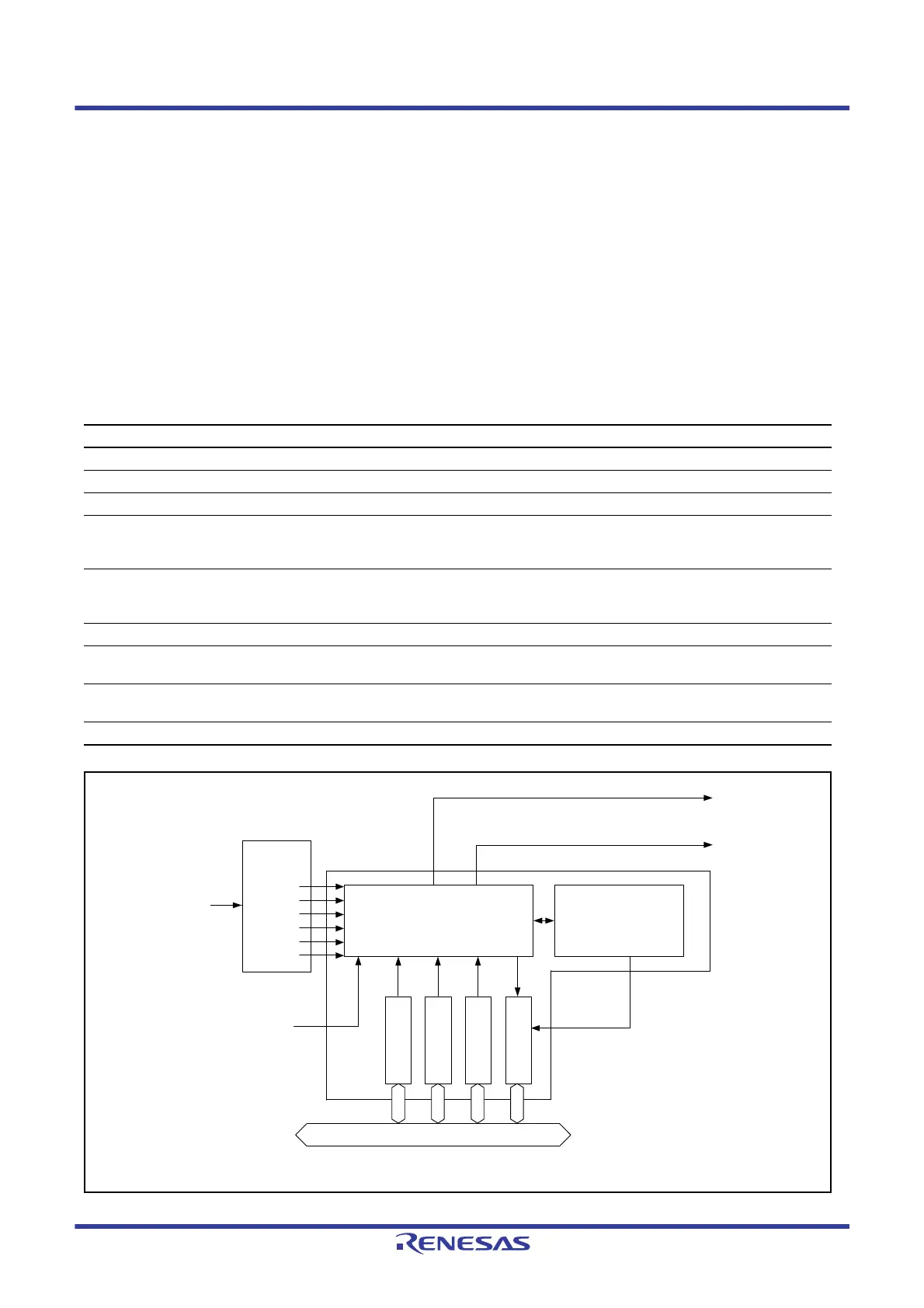

Table 30.1 lists the specifications of the WDT and Figure 30.1 shows a block diagram of the WDT.

Figure 30.1 WDT Block Diagram

Table 30.1 WDT Specifications

Item Specifications

Count source Peripheral module clock (PCLK)

Clock division ratio Divide by 4, 64, 128, 512, 2048, or 8192

Counter operation Counting down using a 14-bit down-counter

Conditions for starting the counter

Auto-start mode: Counting automatically starts after a reset is released

Register start mode: Counting is started by refresh operation (writing 00h and then FFh to the

WDTRR register)

Conditions for stopping the

counter

Reset (the down-counter and other registers return to their initial values)

In low power consumption states

A counter underflows or a refresh error occurs (only in register start mode)

Window function Window start and end positions can be specified (refresh-permitted and refresh-prohibited periods)

Watchdog timer

Reset sources

Down-counter underflows

Refreshing outside the refresh-permitted period (refresh error)

Non-maskable interrupt sources

Down-counter underflows

Refreshing outside the refresh-permitted period (refresh error)

Reading the counter value The down-counter value can be read by the WDTSR register.

Internal peripheral bus

WDT control circuit 14-bit down-counter

WDTRR: WDT refresh register

WDTCR: WDT control register

WDTSR: WDT status register

WDTRCR: WDT reset control register

WDT reset

Interrupt request (WUNI)

Option function select register 0

(OFS0)

PCLK/4

PCLK/64

PCLK/512

PCLK/128

PCLK/2048

PCLK/8192

PCLK

Clock

frequency

divider

WDTRCR

WDTSR

WDTCR

WDTRR

Loading...

Loading...