R01UH0823EJ0100 Rev.1.00 Page 1224 of 1823

Jul 31, 2019

RX23W Group 36. CAN Module (RSCAN)

36.2.34 Receive FIFO Control Register m (RFCCm) (m = 0, 1)

RFE Bit (Receive FIFO Buffer Enable)

Setting the RFE bit to 1 makes receive FIFO buffers available. Setting this bit to 0 sets the RFSTSm.RFEMP flag to 1

(the receive FIFO buffer contains no unread message (buffer empty)). Modify this bit only in global operating mode or

global test mode.

RFIE Bit (Receive FIFO Interrupt Enable)

Setting the RFIE bit to 1 enables receive FIFO interrupts. Modify this bit when the RFE bit is set to 0 (no receive FIFO

buffer is used).

RFDC[2:0] Bits (Receive FIFO Buffer Depth Configuration)

These bits are used to select the number of messages that can be stored in a single receive FIFO buffer. If these bits are

set to 000b, do not use any receive FIFO buffer. Modify these bits only in global reset mode.

RFIM Bit (Receive FIFO Interrupt Source Select)

This bit is used to select a FIFO interrupt source. Modify this bit only in global reset mode.

Address(es): RSCAN.RFCC0 000A 8338h, RSCAN.RFCC1 000A 833Ah

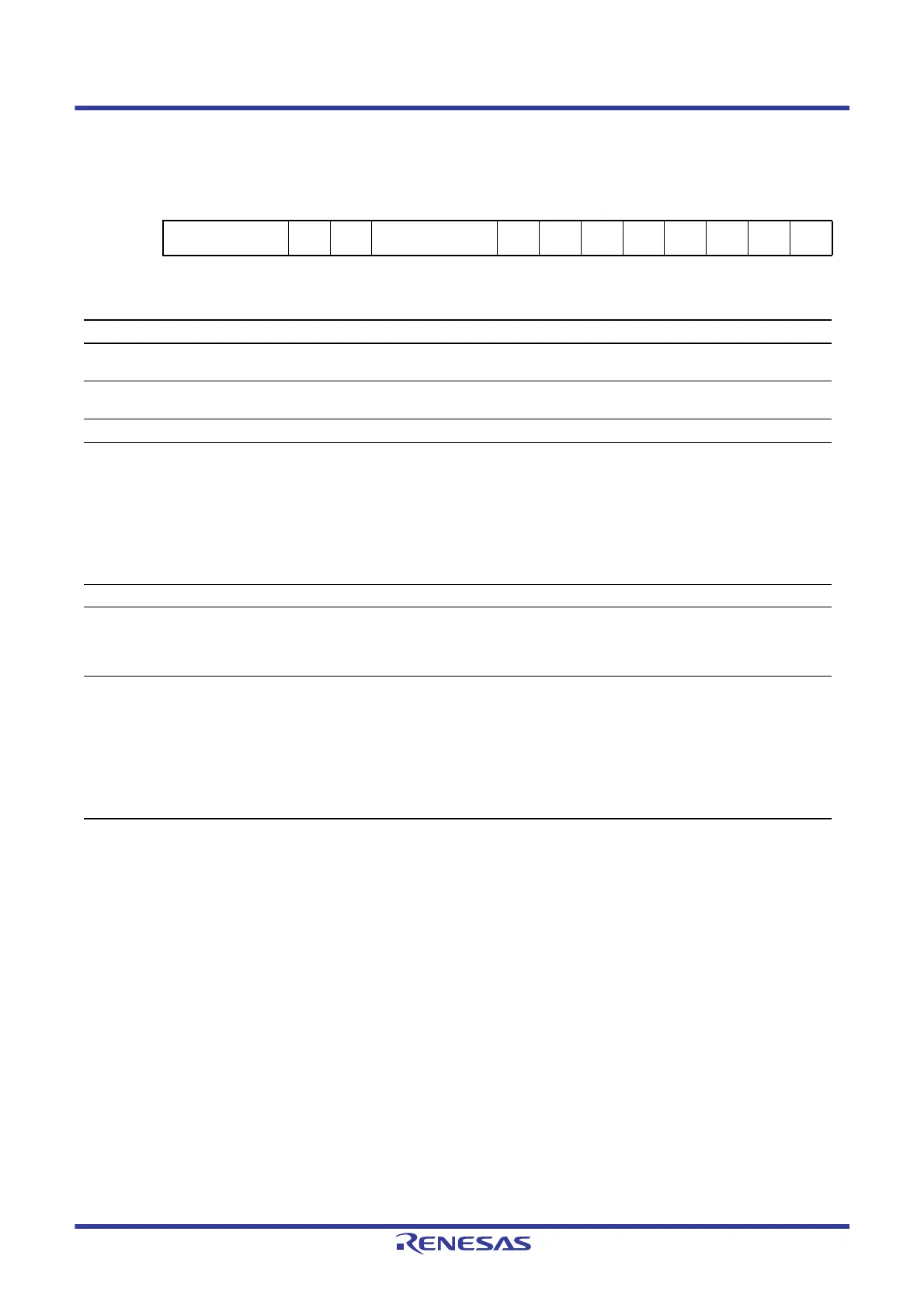

b15 b14 b13 b12 b11 b10 b9 b8 b7 b6 b5 b4 b3 b2 b1 b0

RFIGCV[2:0] RFIM— RFDC[2:0] ——————RFIERFE

Value after reset:

0000000000000000

Bit Symbol Bit Name Description R/W

b0 RFE Receive FIFO Buffer Enable 0: No receive FIFO buffer is used.

1: Receive FIFO buffers are used.

R/W

b1 RFIE Receive FIFO Interrupt Enable 0: Receive FIFO interrupt is disabled.

1: Receive FIFO interrupt is enabled.

R/W

b7 to b2 — Reserved These bits are read as 0. The write value should be 0. R/W

b10 to b8 RFDC[2:0] Receive FIFO Buffer Depth

Configuration

b10 b8

0 0 0: 0 messages

0 0 1: 4 messages

0 1 0: 8 messages

0 1 1: 16 messages

1 0 0: Setting prohibited

1 0 1: Setting prohibited

1 1 0: Setting prohibited

1 1 1: Setting prohibited

R/W

b11 — Reserved This bit is read as 0. The write value should be 0. R/W

b12 RFIM Receive FIFO Interrupt Source

Select

0: An interrupt occurs when the condition set by the

RFIGCV[2:0] bits is met.

1: An interrupt occurs each time a message has been

received.

R/W

b15 to b13 RFIGCV[2:0] Receive FIFO Interrupt Request

Timing Select

b15 b13

0 0 0: When FIFO is 1/8 full.

0 0 1: When FIFO is 2/8 full.

0 1 0: When FIFO is 3/8 full.

0 1 1: When FIFO is 4/8 full.

1 0 0: When FIFO is 5/8 full.

1 0 1: When FIFO is 6/8 full.

1 1 0: When FIFO is 7/8 full.

1 1 1: When FIFO is full.

R/W

Loading...

Loading...