R01UH0823EJ0100 Rev.1.00 Page 1170 of 1823

Jul 31, 2019

RX23W Group 35. I

2

C-bus Interface (RIICa)

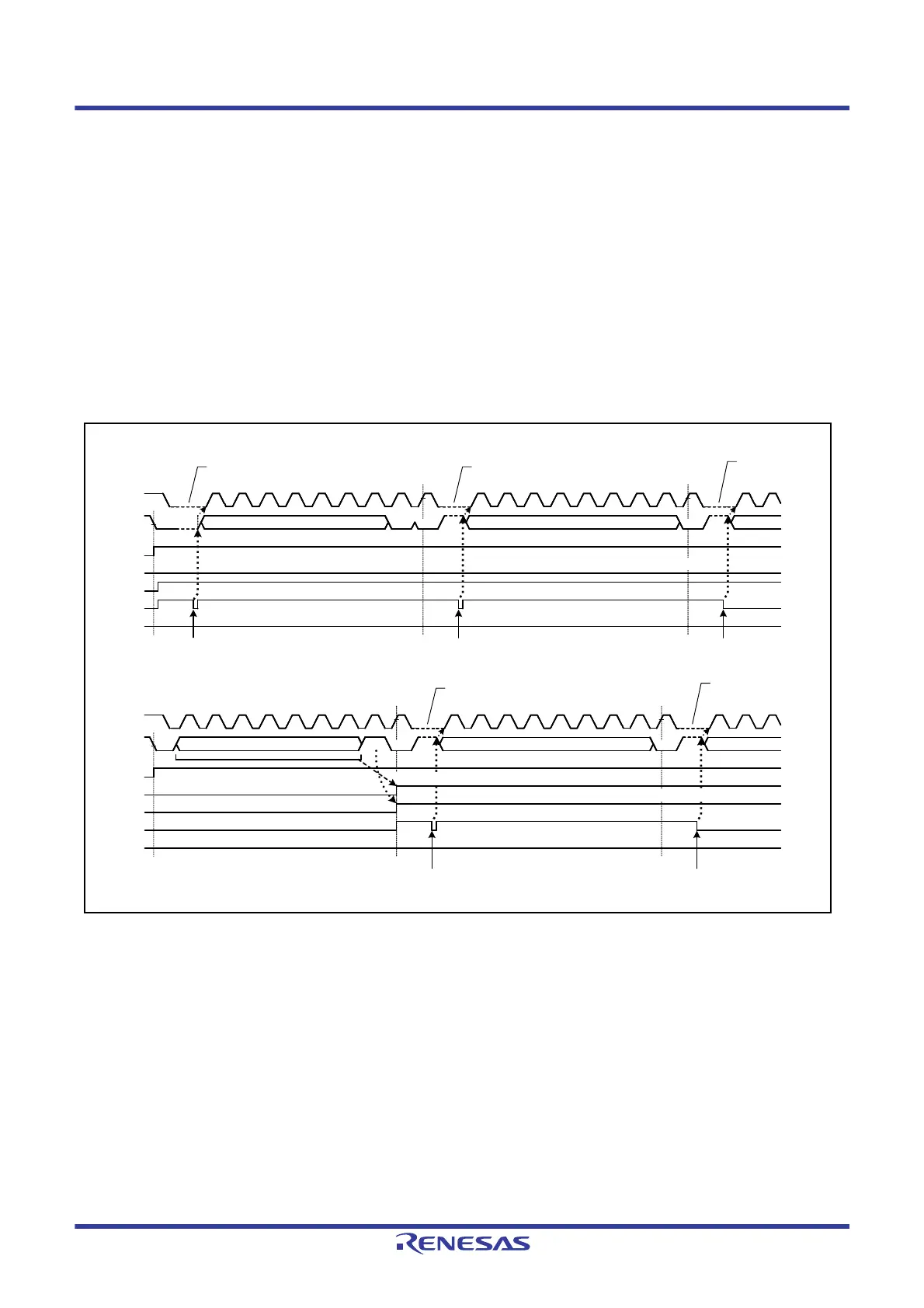

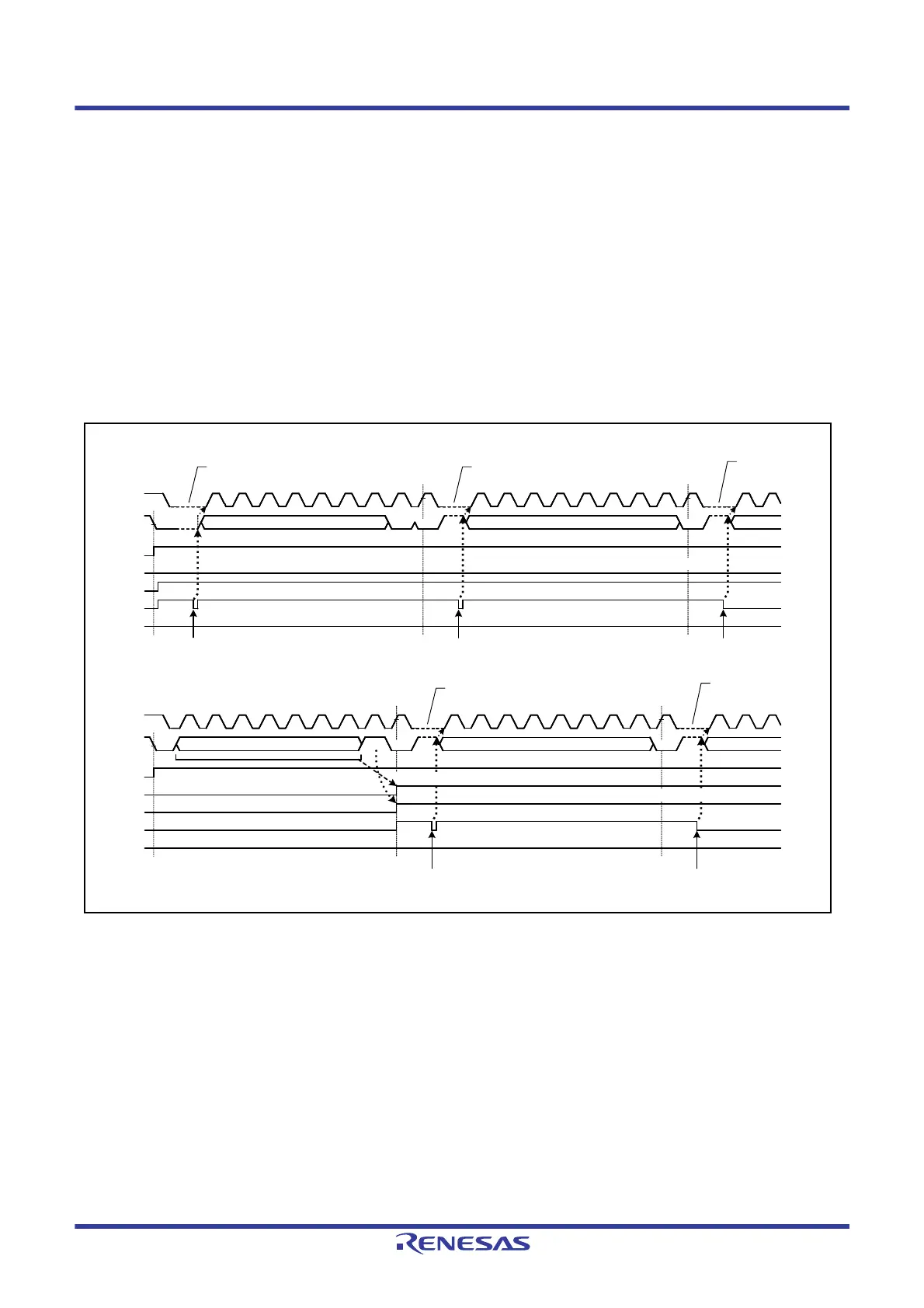

35.8 Automatic Low-Hold Function for SCL

35.8.1 Function to Prevent Wrong Transmission of Transmit Data

If the shift register (ICDRS) is empty when data have not been written to the I

2

C-bus transmit data register (ICDRT) with

the RIIC in transmission mode (ICCR2.TRS bit is 1), the SCL0 line is automatically held at the low level over the

intervals shown below. This low-hold period is extended until data for transmission have been written, which prevents

the unintended transmission of erroneous data.

Master transmit mode

Low-level interval after a start condition or restart condition is issued

Low-level interval between the ninth clock cycle of one transfer and the first clock cycle of the next

Slave transmit mode

Low-level interval between the ninth clock cycle of one transfer and the first clock cycle of the next

Figure 35.30 Automatic Low-Hold Operation in Transmit Mode

8

R

9

ACK

TDRE

AASy

TRS

BBSY

RDRF

S 1 234567 234567 8 9

ACK

23

[Master transmit mode]

[Slave transmit mode]

TDRE

AASy

TRS

BBSY

RDRF

S 234567 234567 8 9

ACK

8

W

9

ACK

21 1 1

11

Data (DATA 1)

7-bit slave address

Data (DATA 1)

7-bit slave address

Write data to ICDRT register

(DATA 1)

Write data to ICDRT register

(DATA 2)

Write data to ICDRT register

(DATA 2)

Write data to ICDRT register

(DATA 1)

Write data to ICDRT register

(7-bit address + W)

Transmit data (7-bit address + W) Transmit data (DATA 1) Transmit data (DATA 2)

Transmit data (DATA 1)

Address match

Automatic low-hold (to prevent wrong transmission)

Automatic low-hold

(to prevent wrong

transmission)

Automatic low-hold

(to prevent wrong

transmission)

Automatic low-hold (to prevent wrong transmission)Automatic low-hold (to prevent wrong transmission)

Transmit data (DATA 2)

Loading...

Loading...