R01UH0823EJ0100 Rev.1.00 Page 496 of 1823

Jul 31, 2019

RX23W Group 23. Multi-Function Timer Pulse Unit 2 (MTU2a)

23.2.8 Timer A/D Converter Start Request Control Register (TADCR)

Note: The TADCR register must not be accessed in 8-bit units; it should be accessed in 16-bit units.

Note 1. When interrupt skipping is disabled (the TITCR.T3AEN and T4VEN bits are set to 0 or the interrupt skipping count setting bits

(T3ACOR[2:0] and T4VCOR[2:0]) in the TITCR register are set to 000b), do not link A/D converter start requests with interrupt

skipping operation (set the TADCR.ITA3AE, ITA4VE, ITB3AE, and ITB4VE bits to 0).

Note 2. If link with interrupt skipping is enabled while interrupt skipping is disabled, A/D converter start requests will not be issued.

Note 3. Set b6 and b4 to b0 to 0 when complementary PWM mode is not selected.

The TADCR register enables or disables A/D converter start requests and specifies whether to link A/D converter start

requests with interrupt skipping operation.

Address(es): MTU4.TADCR 000D 0A40h

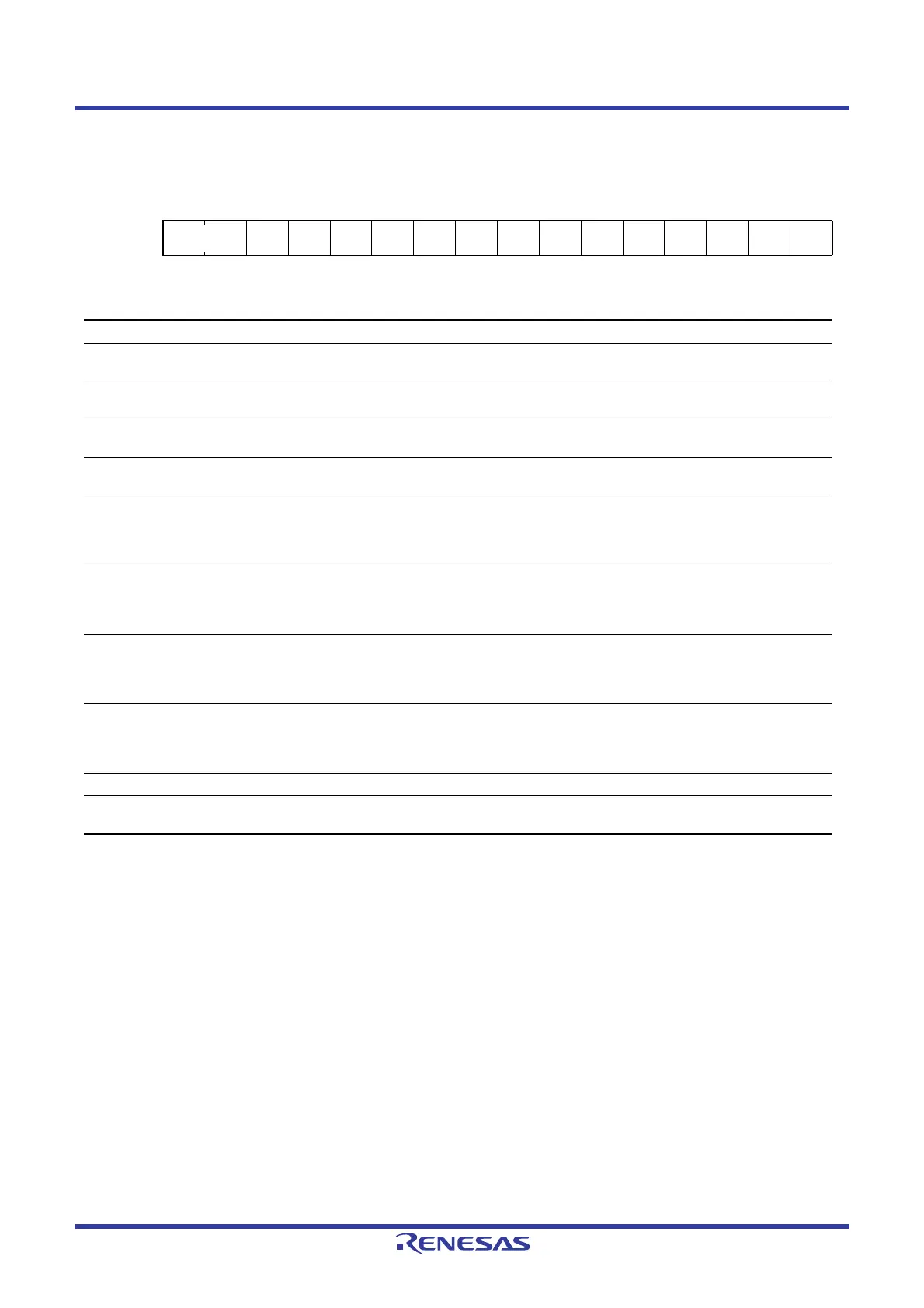

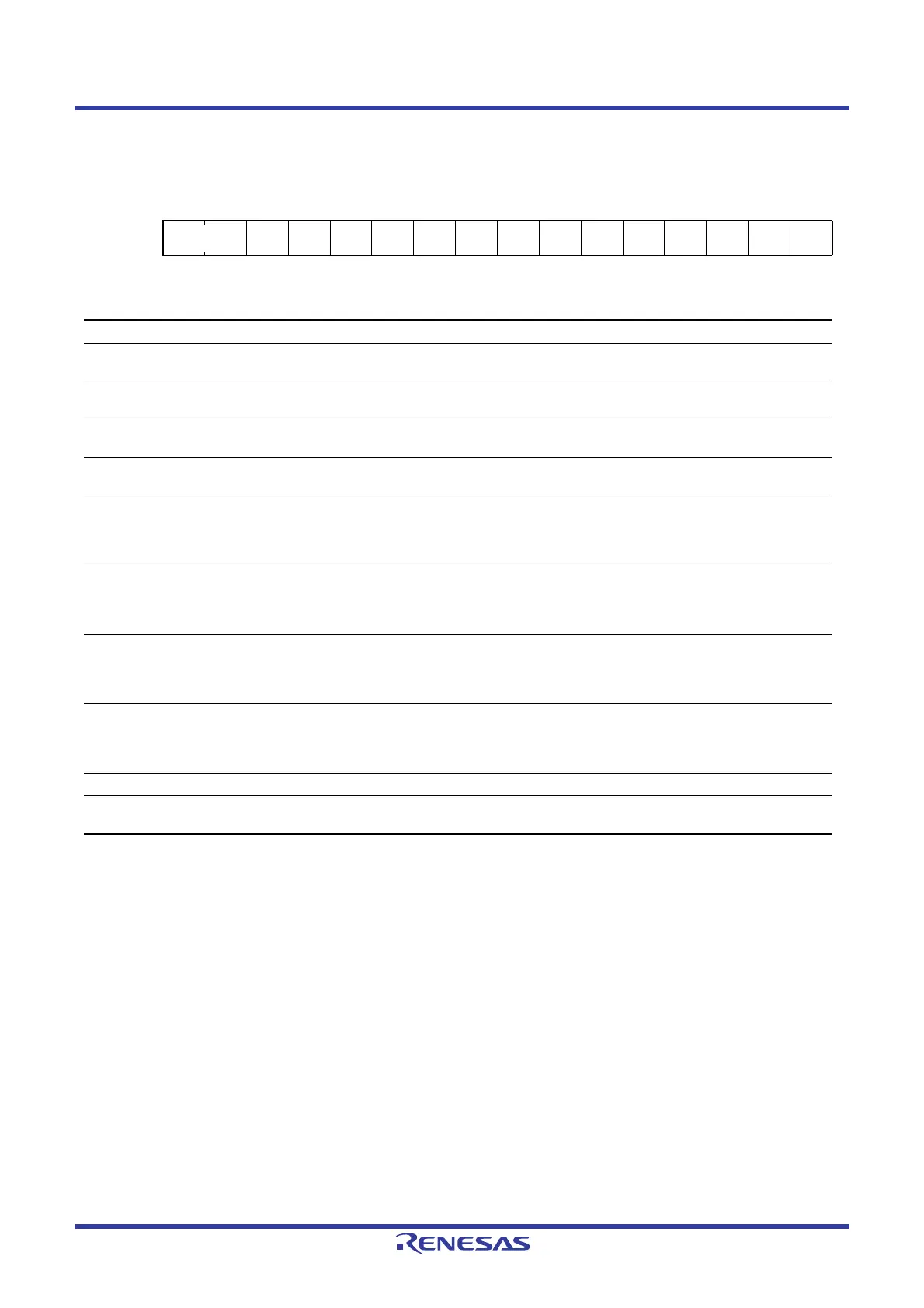

b15 b14 b13 b12 b11 b10 b9 b8 b7 b6 b5 b4 b3 b2 b1 b0

BF[1:0] ——————UT4AEDT4AEUT4BEDT4BEITA3AEITA4VEITB3AEITB4VE

Value after reset:

0000000000000000

Bit Symbol Bit Name Description R/W

b0 ITB4VE TCIV4 Interrupt Skipping Link Enable*

1,

*

2,

*

3

0: TCIV4 interrupt skipping is not linked

1: TCIV4 interrupt skipping is linked

R/W

b1 ITB3AE TGIA3 Interrupt Skipping Link Enable*

1,

*

2,

*

3

0: TGIA3 interrupt skipping is not linked

1: TGIA3 interrupt skipping is linked

R/W

b2 ITA4VE TCIV4 Interrupt Skipping Link Enable*

1,

*

2,

*

3

0: TCIV4 interrupt skipping is not linked

1: TCIV4 interrupt skipping is linked

R/W

b3 ITA3AE TGIA3 Interrupt Skipping Link Enable*

1,

*

2,

*

3

0: TGIA3 interrupt skipping is not linked

1: TGIA3 interrupt skipping is linked

R/W

b4 DT4BE Down-Count TRG4BN Enable*

3

0: A/D converter start requests (TRG4BN) disabled

during MTU4.TCNT down-count operation

1: A/D converter start requests (TRG4BN) enabled

during MTU4.TCNT down-count operation

R/W

b5 UT4BE Up-Count TRG4BN Enable 0: A/D converter start requests (TRG4BN) disabled

during MTU4.TCNT up-count operation

1: A/D converter start requests (TRG4BN) enabled

during MTU4.TCNT up-count operation

R/W

b6 DT4AE Down-Count TRG4AN Enable*

3

0: A/D converter start requests (TRG4AN) disabled

during MTU4.TCNT down-count operation

1: A/D converter start requests (TRG4AN) enabled

during MTU4.TCNT down-count operation

R/W

b7 UT4AE Up-Count TRG4AN Enable 0: A/D converter start requests (TRG4AN) disabled

during MTU4.TCNT up-count operation

1: A/D converter start requests (TRG4AN) enabled

during MTU4.TCNT up-count operation

R/W

b13 to b8 — Reserved These bits are read as 0. The write value should be 0. R/W

b15, b14 BF[1:0] MTU4.TADCOBRA/TADCOBRB Transfer

Timing Select

Refer to Table 23.26 for details. R/W

Loading...

Loading...