R01UH0823EJ0100 Rev.1.00 Page 1677 of 1823

Jul 31, 2019

RX23W Group 50. Flash Memory (FLASH)

50.4.17 Flash Status Register 1 (FSTATR1)

This register is a status register used to confirm the result of executing a software command. Each flag is set to 0 when

the next software command is executed.

FRDY Flag (Flash Ready Flag)

This flag is used to confirm whether a software command is executed.

This flag becomes 1 when processing of the executed software command or the forced stop processing is completed, and

this flag becomes 0 when setting the FCR.OPST bit to 0.

Also, an interrupt (FRDYI) is generated when this flag becomes 1.

EXRDY Flag (Extra Area Ready Flag)

This flag is used to confirm whether a software command for the extra area is executed.

This flag is set to 1 when processing of the executed software command is completed, and 0 when the FEXCR.OPST bit

is set to 0.

Also, an interrupt (FRDYI) is generated when this flag becomes 1.

Address(es): FLASH.FSTATR1 007F C12Ch

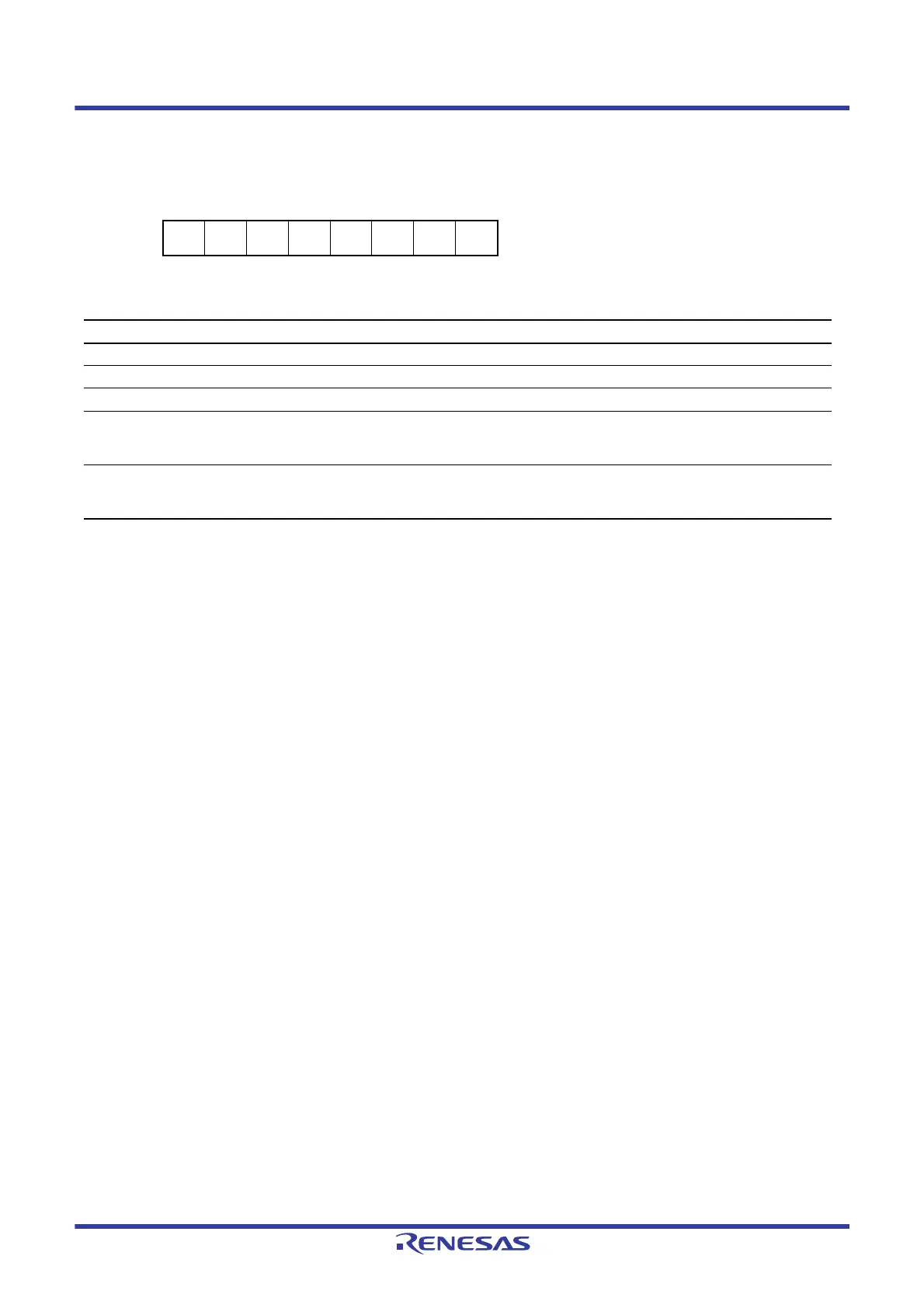

b7 b6 b5 b4 b3 b2 b1 b0

EXRDYFRDY——————

Value after reset:

00000100

Bit Symbol Bit Name Description R/W

b1, b0 — Reserved These bits are read as 0. R

b2 — Reserved This bit is read as 1. R

b5 to b3 — Reserved These bits are read as 0. R

b6 FRDY Flash Ready Flag 0: Other than below

1: 00h can be written to the FCR register (processing to

complete the software command).

R

b7 EXRDY Extra Area Ready Flag 0: Other than below

1: 00h can be written to the FEXCR register (processing to

complete the software command).

R

Loading...

Loading...