R01UH0823EJ0100 Rev.1.00 Page 386 of 1823

Jul 31, 2019

RX23W Group 19. Data Transfer Controller (DTCa)

19.2.8 DTC Vector Base Register (DTCVBR)

The DTCVBR register is used to set the base address for calculating the address to which the DTC vector is allocated.

Writing to the upper 4 bits (b31 to b28) is ignored, and the address of this register is extended by the value specified by

b27. The lower 10 bits are reserved and the values are fixed to 0. Write 0 to the lower 10 bits if necessary.

It can be set in the range of 0000 0000h to 07FF FC00h and F800 0000h to FFFF FC00h in 1-Kbyte units.

19.2.9 DTC Address Mode Register (DTCADMOD)

DTCADMOD register is used to specify the area accessible by the DTC.

SHORT Bit (Short-Address Mode Set)

This bit is used to select address mode of registers SAR and DAR.

Full-address mode allows the DTC to access to a 4-Gbyte space (0000 0000h to FFFF FFFFh).

Short-address mode allows the DTC to access to a 16-Mbyte space (0000 0000h to 007F FFFFh and FF80 0000h to

FFFF FFFFh).

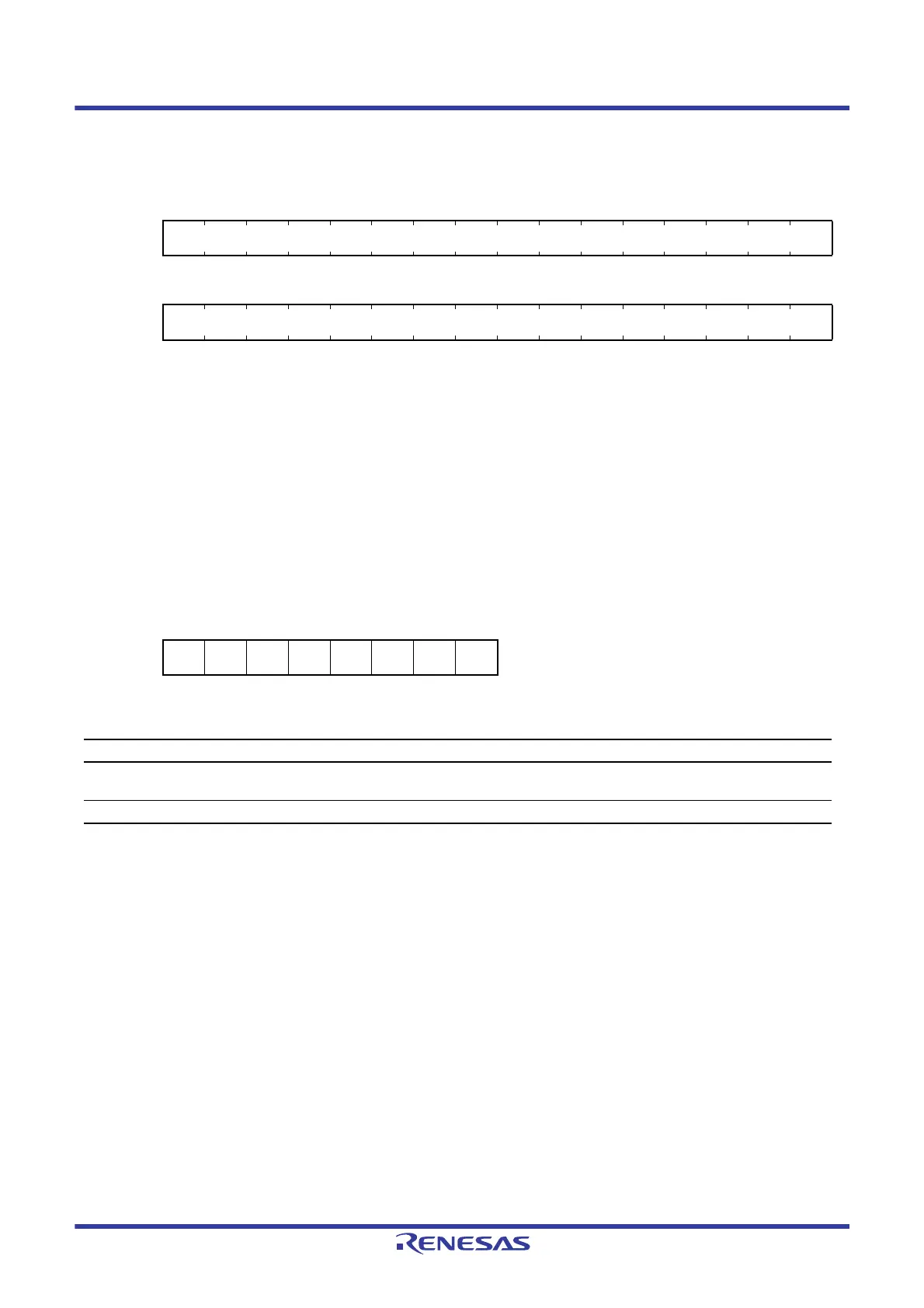

Address(es): DTC.DTCVBR 0008 2404h

b31 b30 b29 b28 b27 b26 b25 b24 b23 b22 b21 b20 b19 b18 b17 b16

Value after reset:

0000000000000000

b15 b14 b13 b12 b11 b10 b9 b8 b7 b6 b5 b4 b3 b2 b1 b0

Value after reset:

0000000000000000

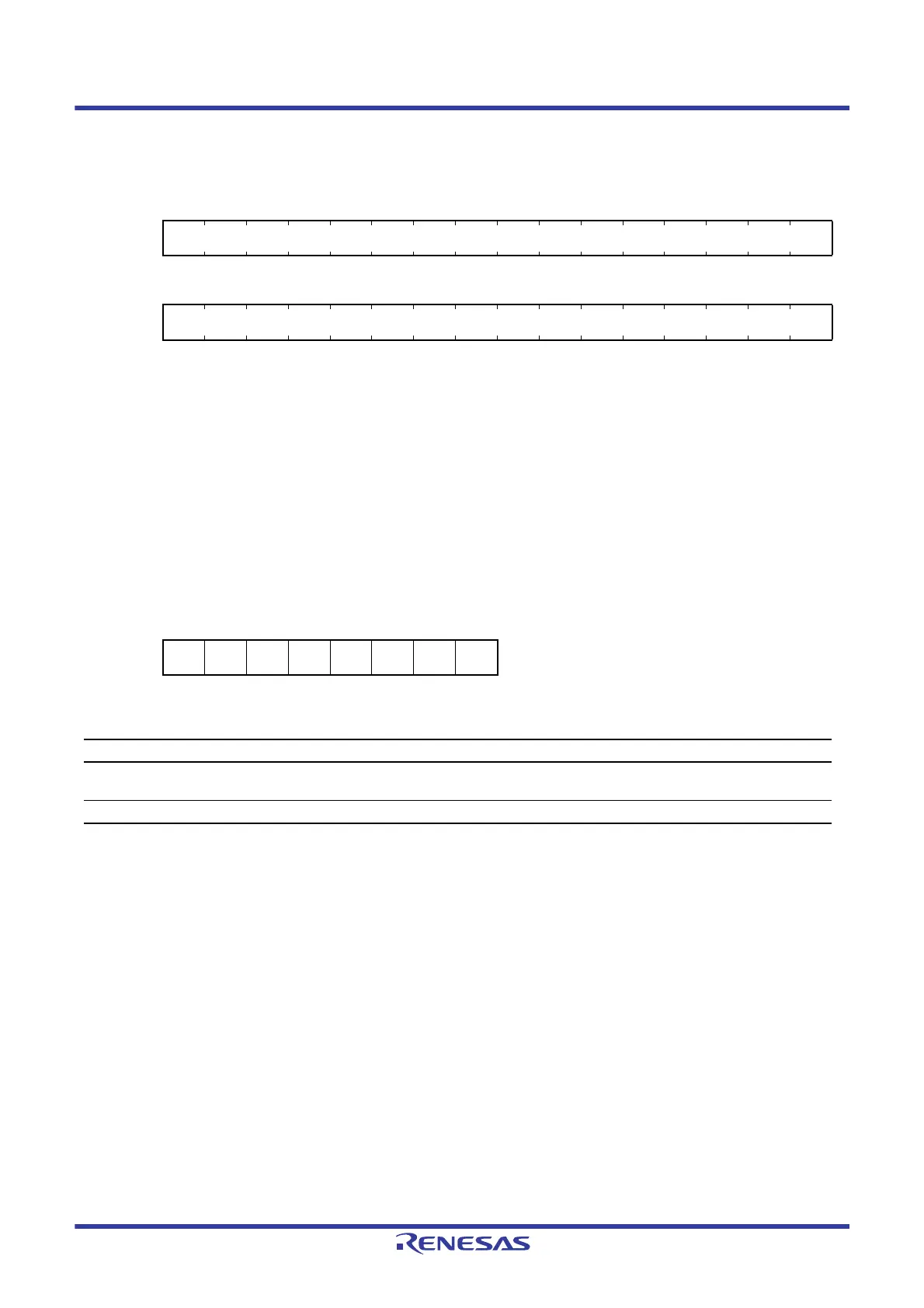

Address(es): DTC.DTCADMOD 0008 2408h

b7 b6 b5 b4 b3 b2 b1 b0

———————SHORT

Value after reset:

00000000

Bit Symbol Bit Name Description R/W

b0 SHORT Short-Address Mode Set 0: Full-address mode

1: Short-address mode

R/W

b7 to b1 — Reserved These bits are read as 0. The write value should be 0. R/W

Loading...

Loading...