R01UH0823EJ0100 Rev.1.00 Page 1538 of 1823

Jul 31, 2019

RX23W Group 44. 12-Bit A/D Converter (S12ADE)

44.2.3 A/D Control Register (ADCSR)

Note 1. Starting A/D conversion using an external pin (asynchronous trigger)

After a high-level signal is input to the external pin (ADTRG0#), write 1 to both the TRGE and EXTRG bits in ADCSR and

change the signals of ADTRG0# to low. Thus the falling edge of ADTRG0# is detected and the scan conversion process is

started. In this case, the pulse width of the low-level input must be at least 1.5 clock cycles of PCLK.

ADCSR sets double trigger mode, A/D conversion start trigger; enables/disables scan end interrupt; selects the scan

mode; and starts or stops A/D conversion.

DBLANS[4:0] Bits (Double Trigger Channel Select)

The DBLANS[4:0] bits select one of the channels for A/D conversion data duplication in double trigger mode. The A/D

conversion results of the analog input of the channel selected by the DBLANS[4:0] bits are stored into the A/D data

register y when conversion is started by the first trigger, and into the A/D data duplication register when started by the

second trigger.

Table 44.5 shows selection of the channel for double triggered operation.

When double trigger mode is selected, channel selection using the ADANSA0 and ADANSA1 registers is invalid, and

the channel selected by the DBLANS[4:0] bits is subjected to A/D conversion instead.

When double trigger mode is used, do not select A/D conversion for the self-diagnosis function, temperature sensor

output, and internal reference voltage (temperature sensor output and internal reference voltage can be selected for A/D

conversion for group B in group scan mode). The DBLANS[4:0] bits should be set while the ADST bit is 0. They should

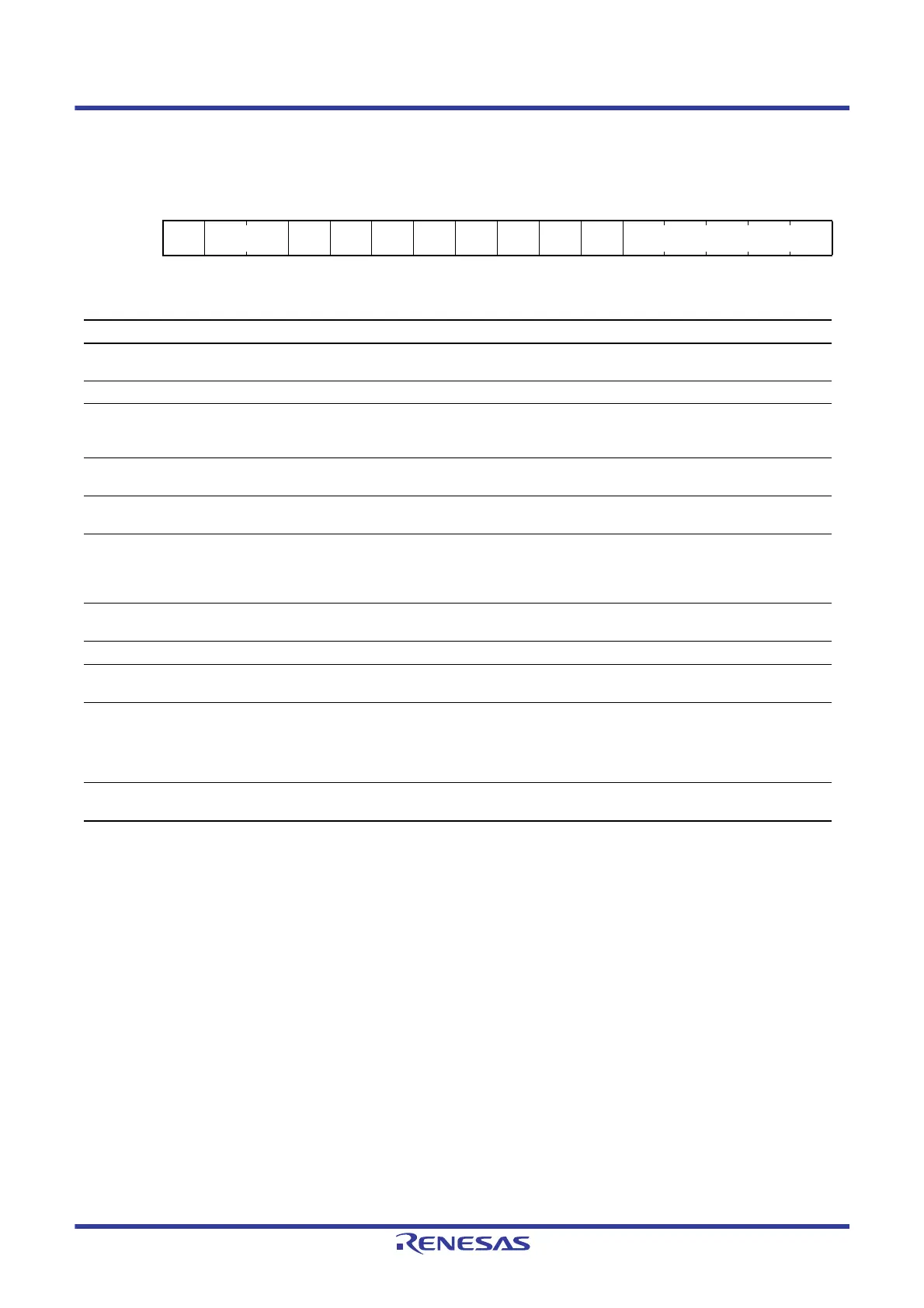

Address(es): S12AD.ADCSR 0008 9000h

b15 b14 b13 b12 b11 b10 b9 b8 b7 b6 b5 b4 b3 b2 b1 b0

ADST ADCS[1:0] ADIE — ADHSC TRGE EXTRG DBLE

GBADI

E

— DBLANS[4:0]

Value after reset:

0000000000000000

Bit Symbol Bit Name Description R/W

b4 to b0 DBLANS[4:0] Double Trigger

Channel Select

These bits select one analog input channel for double triggered operation.

The setting is only effective while double trigger mode is selected.

R/W

b5 — Reserved This bit is read as 0. The write value should be 0. R/W

b6 GBADIE Group B Scan

End Interrupt

Enable

0: Disables GBADI interrupt generation upon group B scan completion.

1: Enables GBADI interrupt generation upon group B scan completion.

R/W

b7 DBLE Double Trigger

Mode Select

0: Deselects double trigger mode.

1: Selects double trigger mode.

R/W

b8 EXTRG Trigger Select

*1

0: A/D conversion is started by synchronous trigger.

1: A/D conversion is started by asynchronous trigger.

R/W

b9 TRGE Trigger Start

Enable

0: Disables A/D conversion to be started by synchronous or asynchronous

trigger.

1: Enables A/D conversion to be started by synchronous or asynchronous

trigger.

R/W

b10 ADHSC A/D Conversion

Select

0: High-speed conversion

1: Low-current conversion

R/W

b11 — Reserved This bit is read as 0. The write value should be 0. R/W

b12 ADIE Scan End

Interrupt Enable

0: Disables S12ADI0 interrupt generation upon scan completion.

1: Enables S12ADI0 interrupt generation upon scan completion.

R/W

b14, b13 ADCS[1:0] Scan Mode

Select

b14 b13

0 0: Single scan mode

0 1: Group scan mode

1 0: Continuous scan mode

1 1: Setting prohibited

R/W

b15 ADST A/D Conversion

Start

0: Stops A/D conversion process.

1: Starts A/D conversion process.

R/W

Loading...

Loading...