R01UH0823EJ0100 Rev.1.00 Page 1539 of 1823

Jul 31, 2019

RX23W Group 44. 12-Bit A/D Converter (S12ADE)

not be set simultaneously when 1 is written to the ADST bit.

To enter A/D-converted value addition/average mode while double trigger mode is set, the channel selected by the

DBLANS[4:0] bits should be selected in the ADANSA0 and ADANSA1 registers.

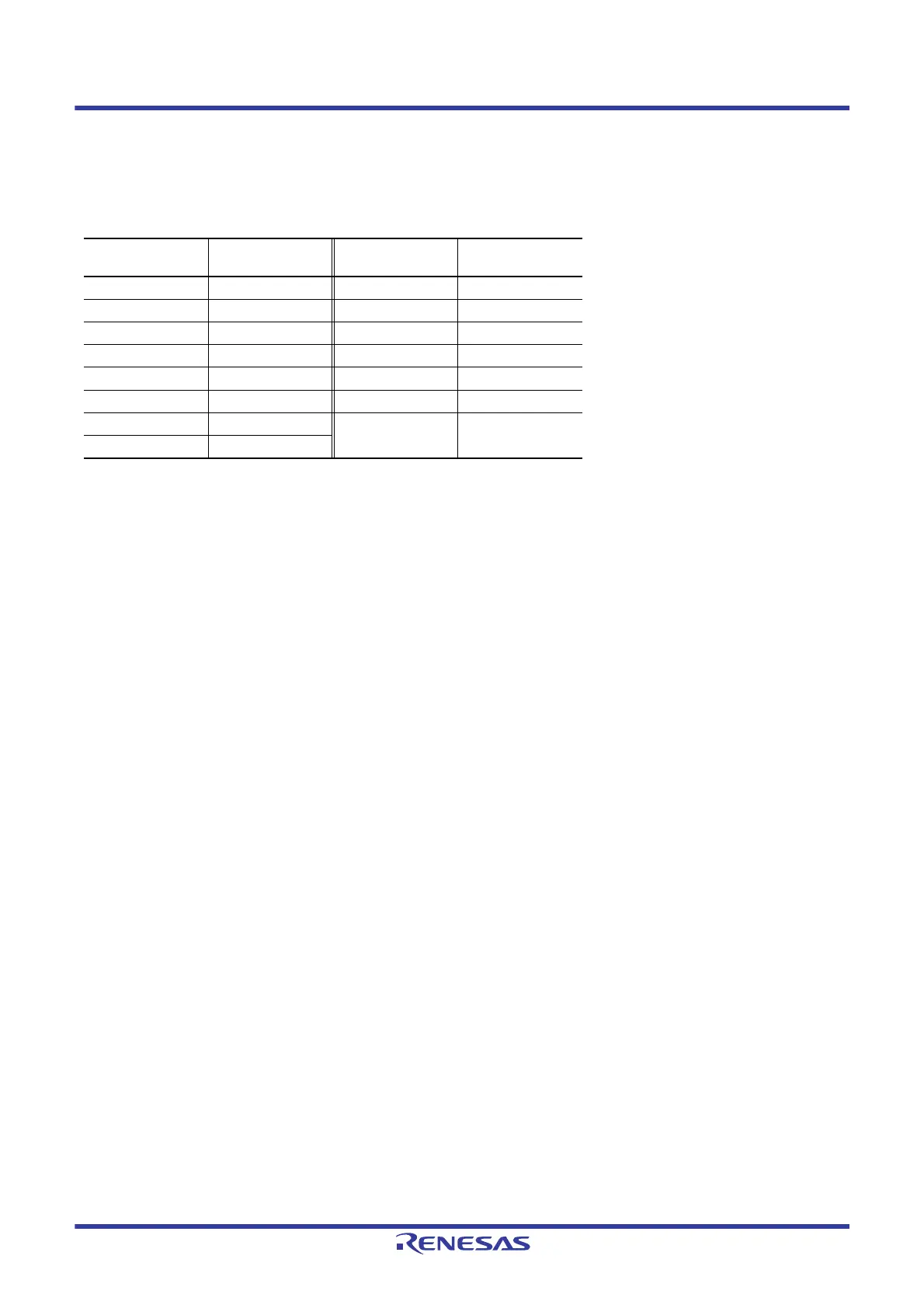

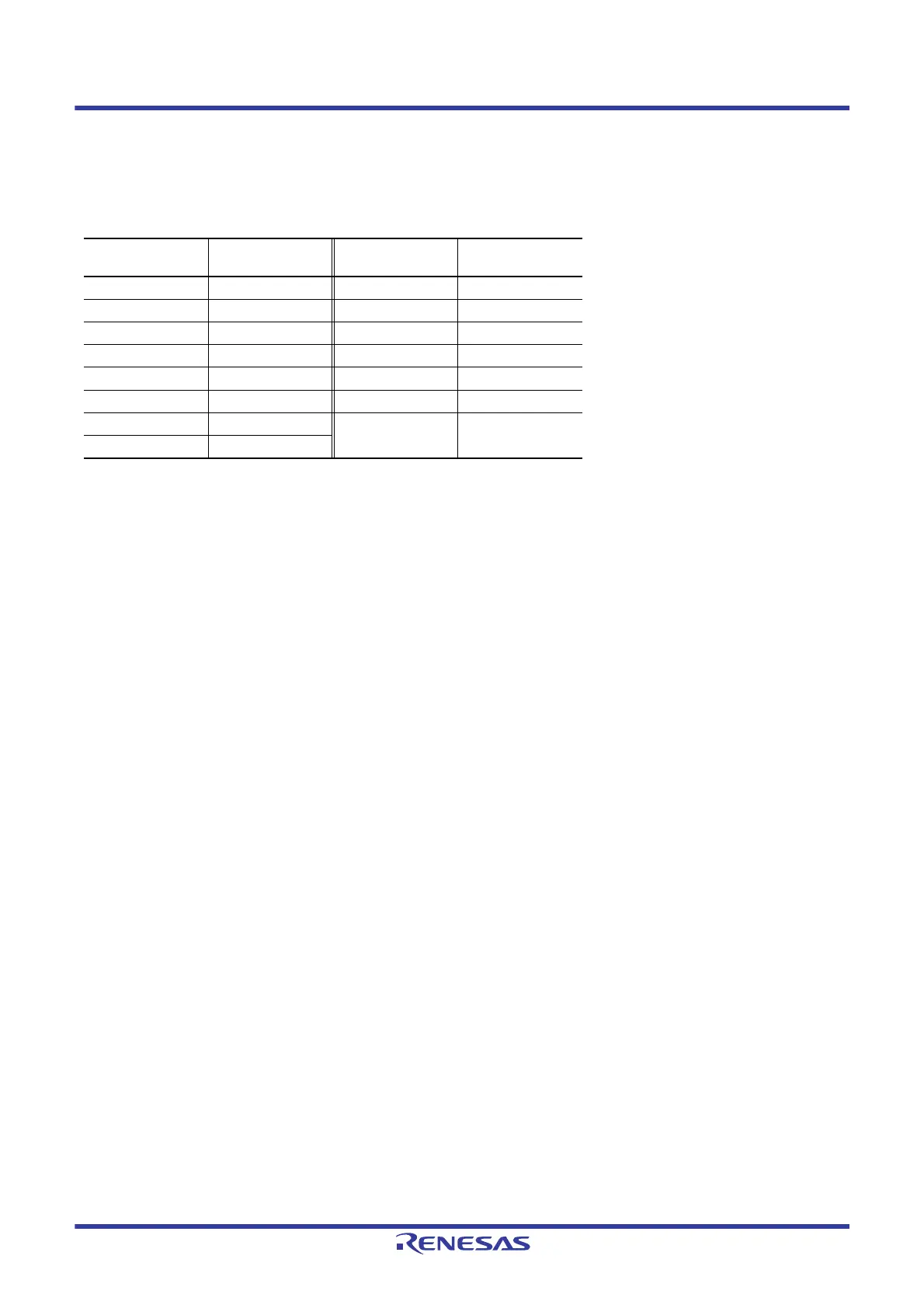

Table 44.5 Relationship between DBLANS[4:0] Bits Settings and Double Trigger Enabled Channels

GBADIE Bit (Group B Scan End Interrupt Enable)

The GBADIE bit enables or disables group B scan end interrupt (GBADI) in group scan mode.

DBLE Bit (Double Trigger Mode Select)

Double trigger mode has a function to store the resulting data of A/D conversion started by the first and second

synchronous triggers into separate registers.

When double trigger mode is selected, channel selection using the ADANSA0 and ADANSA1 registers is invalid and

the channel selected by the DBLANS[4:0] bits is effective instead. Double trigger mode can be only operated by the

synchronous trigger selected by the ADSTRGR.TRSA[5:0] bits. Do not generate an asynchronous or software trigger.

The A/D conversion results started by the first trigger are stored into the A/D data register y and those started by the

second trigger are stored into the A/D data duplication register. In this case, if the ADIE bit is set to 1, the interrupt is

generated not upon completion of the first conversion but upon completion of the second conversion.

In continuous scan mode, double trigger mode should not be selected.

The DBLE bit should be set after the ADST bit has been set to 0.

EXTRG Bit (Trigger Select)

The EXTRG bit selects the synchronous trigger or the asynchronous trigger as the trigger for starting A/D conversion.

TRGE Bit (Trigger Start Enable)

The TRGE bit enables or disables A/D conversion by the synchronous trigger and the asynchronous trigger.

This bit should be set to 1 in group scan mode.

ADHSC Bit (A/D Conversion Select)

The ADHSC bit sets the operating mode of A/D conversion. When modifying this bit, set the 12-bit converter to the

standby state. For the procedure for modifying the ADHSC bit, see

section 44.8.10, ADHSC Bit Rewriting

Procedure

.

ADIE Bit (Scan End Interrupt Enable)

The ADIE bit enables or disables the A/D scan end interrupt (S12ADI0) in scans except for group B scan in group scan

mode.

With double trigger mode deselected, the S12ADI0 interrupt is generated after the first scan is completed if the ADIE bit

is set to 1.

With double trigger mode selected, the S12ADI0 interrupt is generated after the second scan is completed if the ADIE bit

DBLANS[4:0]

Duplication

Channel DBLANS[4:0]

Duplication

Channel

00000b AN000 10000b AN016

00001b AN001 10001b AN017

00010b AN002 10010b AN018

00011b AN003 10011b AN019

00100b AN004 10100b AN020

00101b AN005 11011b AN027

00110b AN006

00111b AN007

Loading...

Loading...