R01UH0823EJ0100 Rev.1.00 Page 1182 of 1823

Jul 31, 2019

RX23W Group 35. I

2

C-bus Interface (RIICa)

35.11.2 Extra SCL Clock Cycle Output Function

In master mode, the RIIC module has a facility for the output of extra SCL clock cycles to release the SDA0 line of the

slave device from being held at the low level due to the master being out of synchronization with the slave device.

This function is mainly used in master mode to release the SDA0 line of the slave device from the state of being fixed to

the low level by including extra cycles of SCL output from the RIIC with single cycles of the SCL clock as the unit if the

RIIC cannot issue a stop condition because the slave device is holding the SDA0 line at the low level. Do not use this

facility in normal situations. Using it when communications are proceeding correctly will lead to malfunctions.

When the ICCR1.CLO bit is set to 1 in master mode, a single cycle of the SCL clock at the frequency corresponding to

the transfer rate settings (settings of the ICMR1.CKS[2:0] bits, and of registers ICBRH and ICBRL) is output as an extra

clock cycle. After output of this single cycle of the SCL clock, the CLO bit is automatically set to 0. Therefore, further

extra clock cycles can be output consecutively by writing 1 to the CLO bit after confirming the CLO bit to be 0.

When the RIIC module is in master mode and the slave device is holding the SDA0 line at the low level because

synchronization with the slave device has been lost due to the effects of noise, etc., the output of a stop condition is not

possible. The facility for output of an extra cycle of the SCL clock can be used to output extra cycles of SCL one by one

to make the slave device release the SDA0 line from being held at the low level, thus recovering the bus from an

unusable state. Release of the SDA0 line by the slave device can be monitored by reading the ICCR1.SDAI bit. After

confirming release of the SDA0 line by the slave device, complete communications by reissuing the stop condition.

Use this facility with the ICFER.MALE bit (master arbitration-lost detection disabled) set to 0. If the MALE bit is set to

1 (master arbitration-lost detection enabled), arbitration is lost when the value of the ICCR1.SDAO bit does not match

the state of the SDA0 line, so take care on this point.

Output conditions for using the ICCR1.CLO bit

When the bus is free (ICCR2.BBSY flag is 0) or in master mode (ICCR2.MST bit is 1 and ICCR2.BBSY flag is 1)

When the communication device does not hold the SCL0 line low

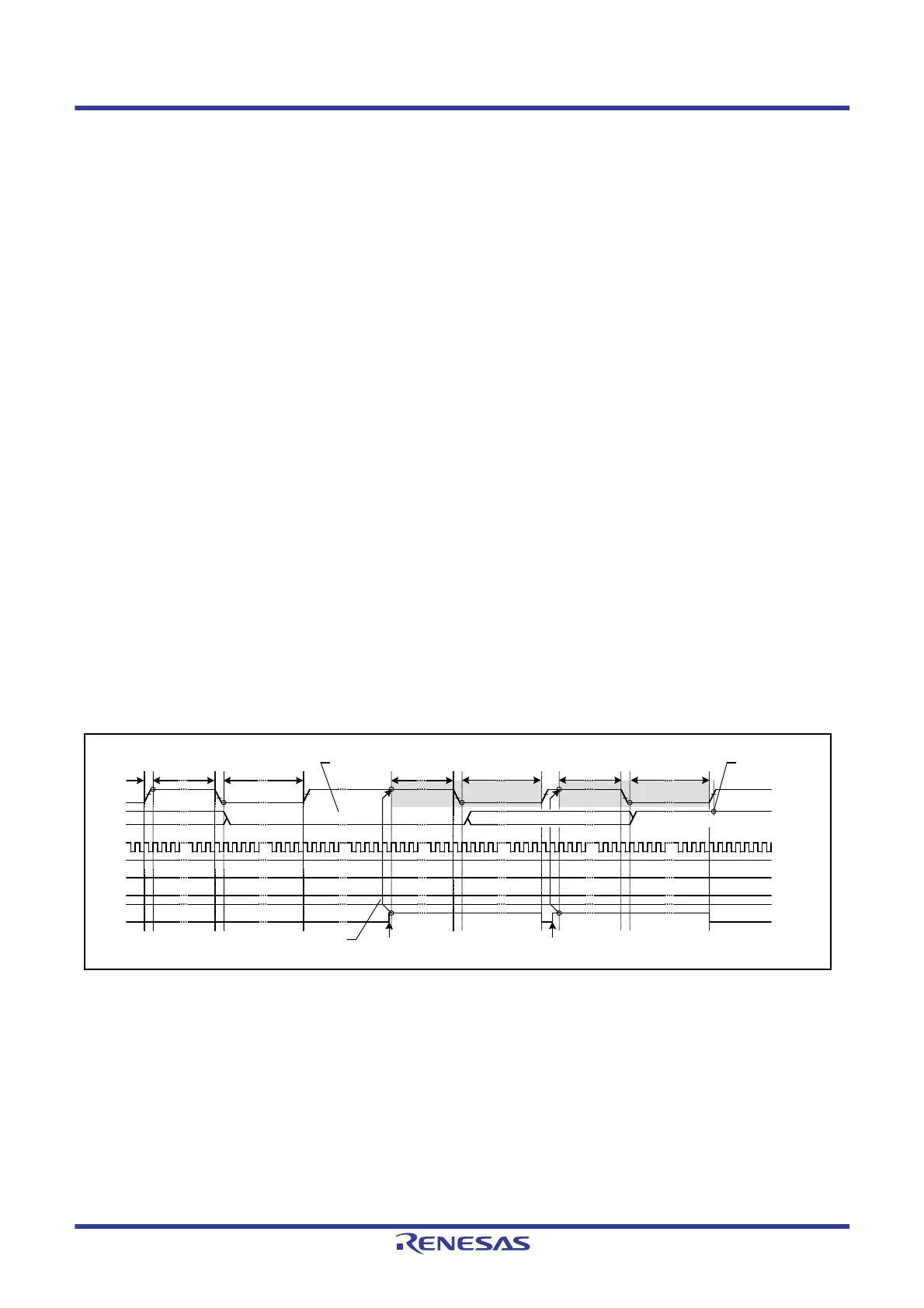

Figure 35.40 shows the operation timing of the extra SCL clock cycle output function (CLO bit).

Figure 35.40 Extra SCL Clock Cycle Output Function (CLO Bit)

Write 1 to CLO bit

Accept CLO output

Write 1 to CLO bit

Data 1

MSB or Next Data

ICBRH ICBRLICBRH

ACK or Data 0

ICBRLICBRLICBRH

9

Extra clock cycle

output

Extra clock cycle

output

TRS

MST

BBSY

IIC

CLO

SCL0

SDA0

Release SDA0 lineSDA0 line is held low due to irregular bits

Loading...

Loading...