R01UH0823EJ0100 Rev.1.00 Page 513 of 1823

Jul 31, 2019

RX23W Group 23. Multi-Function Timer Pulse Unit 2 (MTU2a)

23.2.26 Timer Interrupt Skipping Counters (TITCNT)

Note: To clear the TITCNT counter, set the T3AEN and T4VEN bits in the TITCR register to 0.

The TITCNT counters count the number of interrupt source occurrences for interrupt skipping. The TITCNT counter

retain their values even after stopping the count operation of counters MTU4.TCNT and MTU3.TCNT.

T4VCNT[2:0] Bits (TCIV4 Interrupt Counter)

[Clearing conditions]

When the TITCNT.T4VCNT[2:0] bits match the TITCR.T4VCOR[2:0] bits

When the TITCR.T4VEN bit is set to 0

When the TITCR.T4VCOR[2:0] bits are set to 000b

T3ACNT[2:0] Bits (TGIA3 Interrupt Counter)

[Clearing conditions]

When the TITCNT.T3ACNT[2:0] bits match the TITCR.T3ACOR[2:0] bits

When the TITCR.T3AEN bit is set to 0

When the TITCR.T3ACOR[2:0] bits are set to 000b

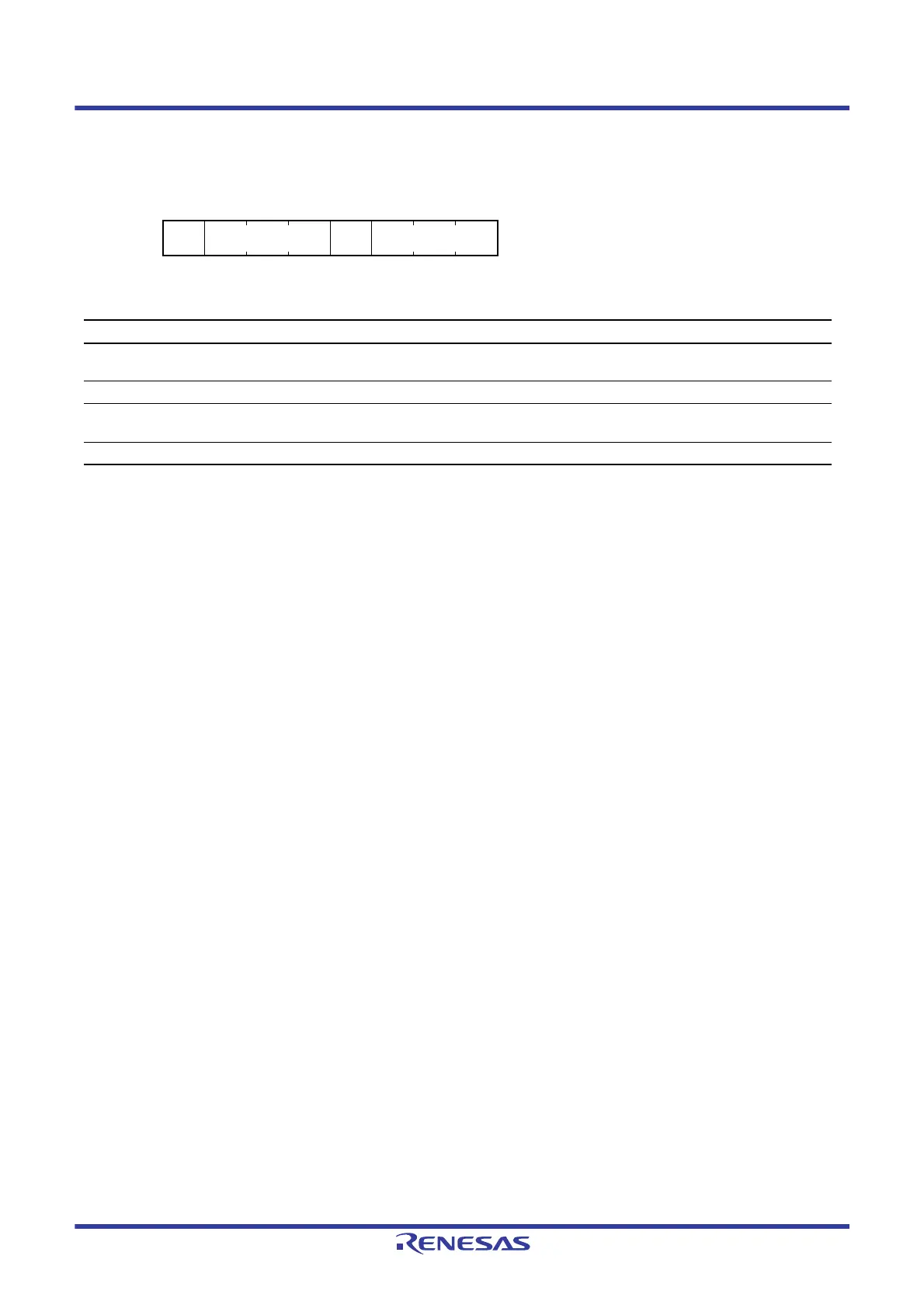

Address(es): MTU.TITCNT 000D 0A31h

b7 b6 b5 b4 b3 b2 b1 b0

— T3ACNT[2:0] — T4VCNT[2:0]

Value after reset:

00000000

Bit Symbol Bit Name Description R/W

b2 to b0 T4VCNT[2:0] TCIV4 Interrupt Counter While the T4VEN bit in TITCR is set to 1, the count in these bits is

incremented every time a TCIV4 interrupt source occurs.

R

b3 — Reserved This bit is read as 0. R

b6 to b4 T3ACNT[2:0] TGIA3 Interrupt Counter While the T3AEN bit in TITCR is set to 1, the count in these bits is

incremented every time a TGIA3 interrupt source occurs.

R

b7 — Reserved This bit is read as 0. R

Loading...

Loading...