R01UH0823EJ0100 Rev.1.00 Page 312 of 1823

Jul 31, 2019

RX23W Group 16. Buses

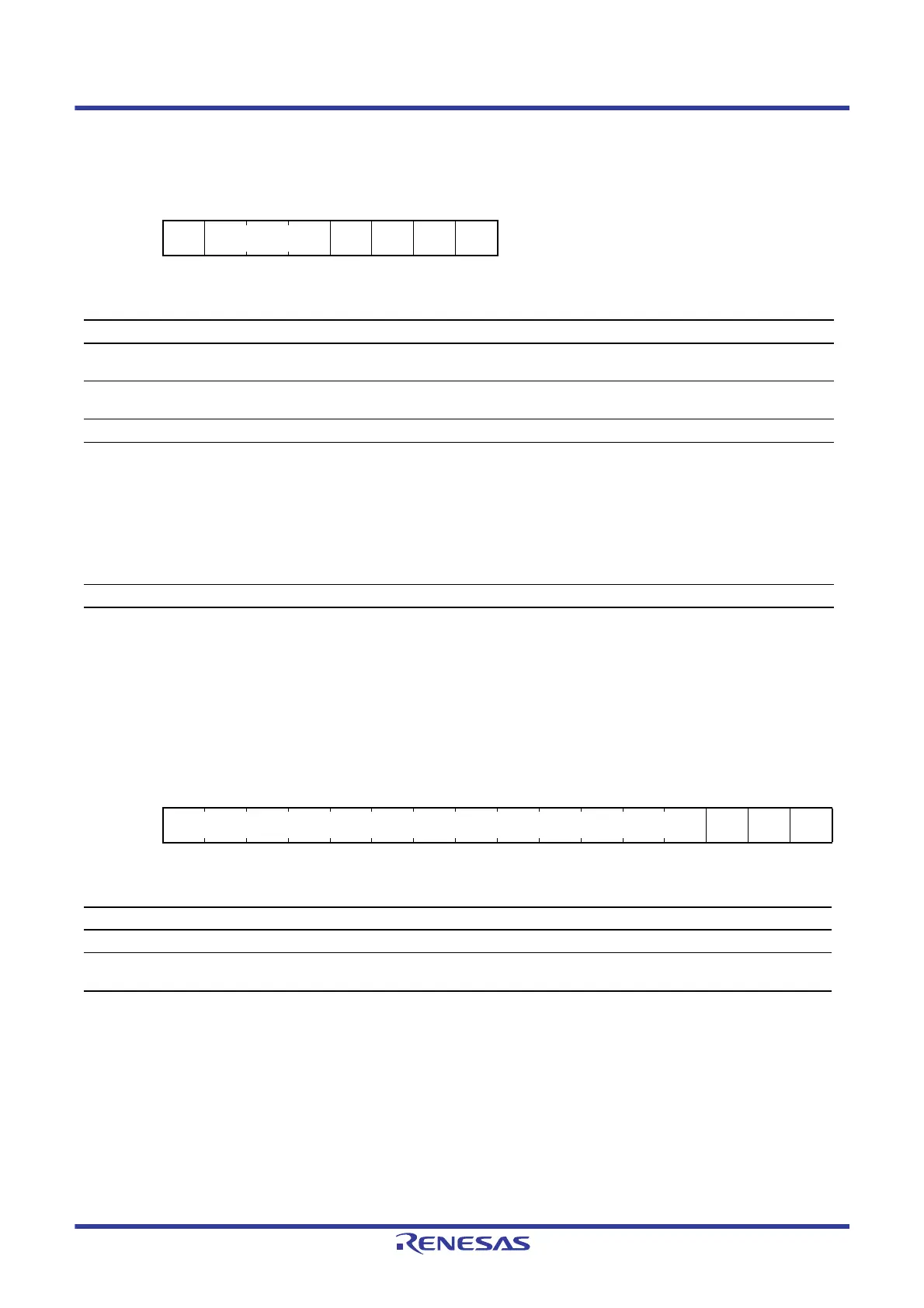

16.3.3 Bus Error Status Register 1 (BERSR1)

MST[2:0] Bits (Bus Master Code)

These bits indicate the bus master that accessed a bus when a bus error occurred.

16.3.4 Bus Error Status Register 2 (BERSR2)

Address(es): 0008 1308h

b7 b6 b5 b4 b3 b2 b1 b0

— MST[2:0] — — TO IA

Value after reset:

00000000

Bit Symbol Bit Name Description R/W

b0 IA Illegal Address Access 0: Illegal address access not made

1: Illegal address access made

R

b1 TO Timeout 0: Timeout not generated

1: Timeout generated

R

b3, b2 — Reserved These bits are read as 0. Writing to these bits has no effect. R

b6 to b4 MST[2:0] Bus Master Code

b6 b4

0 0 0: CPU

0 0 1: Reserved

0 1 0: Reserved

0 1 1: DTC/DMAC

1 0 0: Reserved

1 0 1: Reserved

1 1 0: Reserved

1 1 1: Reserved

R

b7 — Reserved This bit is read as 0. Writing to this bit has no effect. R

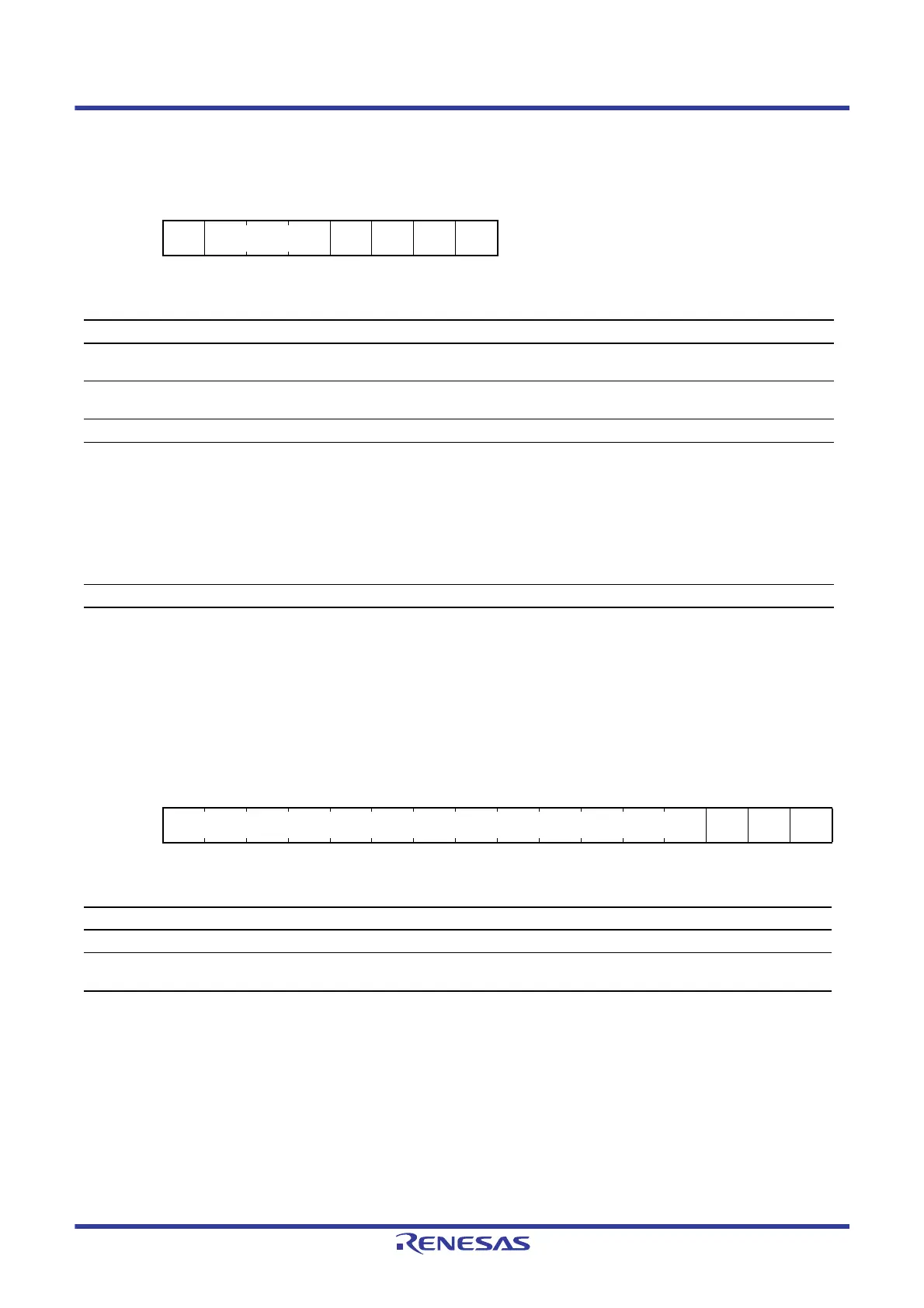

Address(es): 0008 130Ah

b15 b14 b13 b12 b11 b10 b9 b8 b7 b6 b5 b4 b3 b2 b1 b0

ADDR[12:0] — — —

Value after reset:

0000000000000000

Bit Symbol Bit Name Description R/W

b2 to b0 — Reserved These bits are read as 0. Writing to these bits has no effect. R

b15 to b3 ADDR[12:0] Bus Error

Occurrence Address

The upper 13 bits of an address that was accessed when a bus error

occurred (in units of 512 Kbytes).

R

Loading...

Loading...