R01UH0823EJ0100 Rev.1.00 Page 1225 of 1823

Jul 31, 2019

RX23W Group 36. CAN Module (RSCAN)

RFIGCV[2:0] Bits (Receive FIFO Interrupt Request Timing Select)

These bits are used to specify the fraction of the transmit/receive FIFO buffer (the number of messages is selected by the

setting of the RFDC[2:0] bits) that must be filled for the FIFO buffer to generate a receive interrupt request when the

RFIM bit is set to 0.

When the RFDC[2:0] bits are set to 001b (4 messages), set the RFIGCV[2:0] bits to 001b, 011b, 101b, or 111b. Modify

these bits only in global reset mode.

36.2.35 Receive FIFO Status Register m (RFSTSm) (m = 0, 1)

Note 1. Only 0 can be written to this bit, to clear the flag. Writing 1 does not affect the flag value.

RFEMP Flag (Receive FIFO Buffer Empty Status Flag)

This flag becomes 1 when all messages in the receive FIFO buffer have been read. This flag also becomes 1 when the

RFCCm.RFE bit is 0 or in global reset mode.

This flag becomes 0 when even a single received message has been stored in the receive FIFO buffer.

RFFLL Flag (Receive FIFO Buffer Full Status Flag)

This flag becomes 1 when the number of messages stored in the receive FIFO buffer matches the FIFO buffer depth set

by the RFCCm.RFDC[2:0] bits.

If the number of messages stored in the receive FIFO buffer becomes smaller than the FIFO buffer depth set by the

RFCCm.RFDC[2:0] bits, this flag becomes 0. This flag also becomes 0 when the RFCCm.RFE bit is set to 0 (no receive

FIFO buffer is used) or in global reset mode.

RFMLT Flag (Receive FIFO Message Lost Flag)

This flag becomes 1 when it is attempted to store a new message while the receive FIFO buffer is full. In this case, the

new message is discarded.

This flag becomes 0 in global reset mode or by writing 0 to this flag.

Modify this bit only in global operating mode or global test mode.

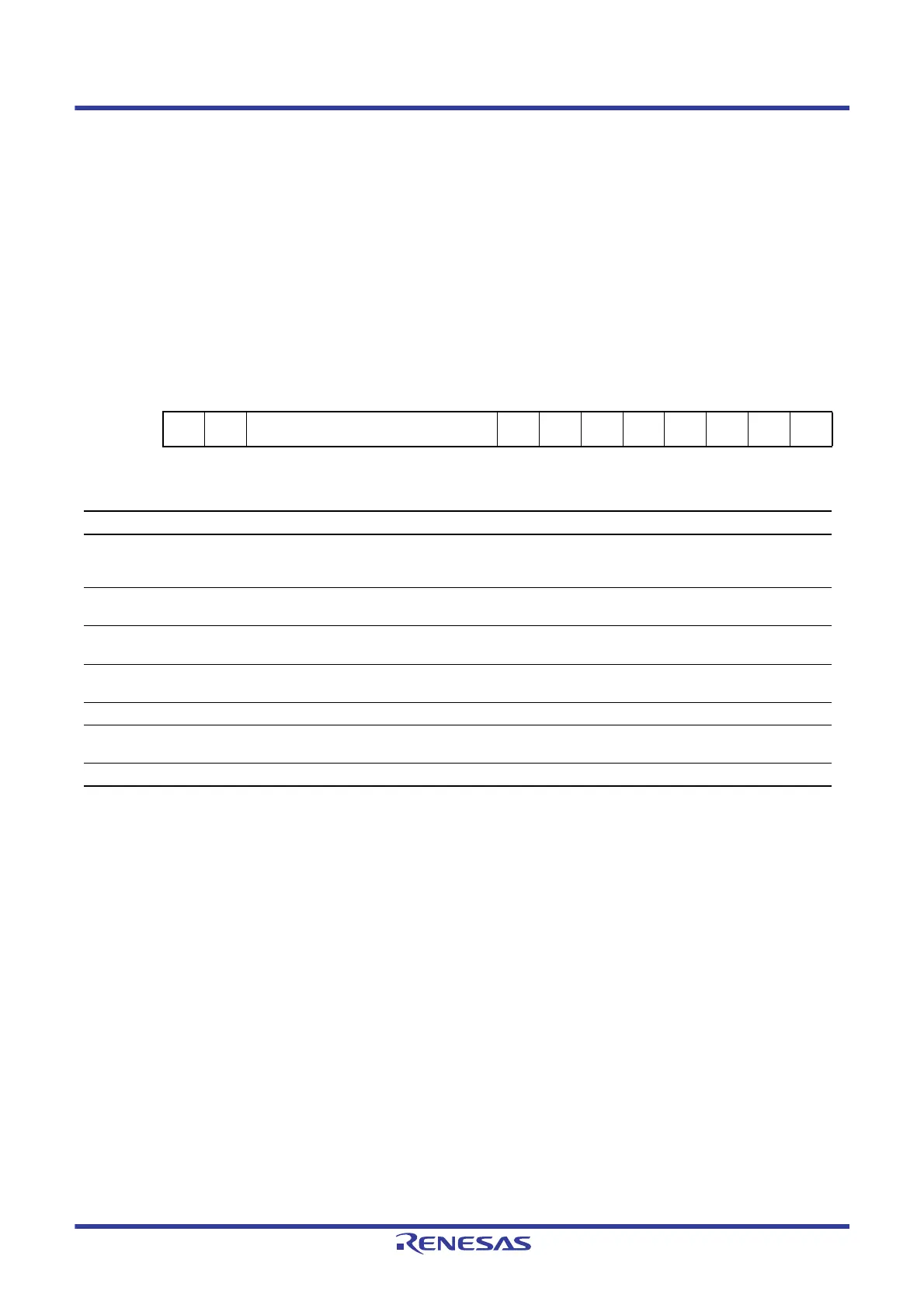

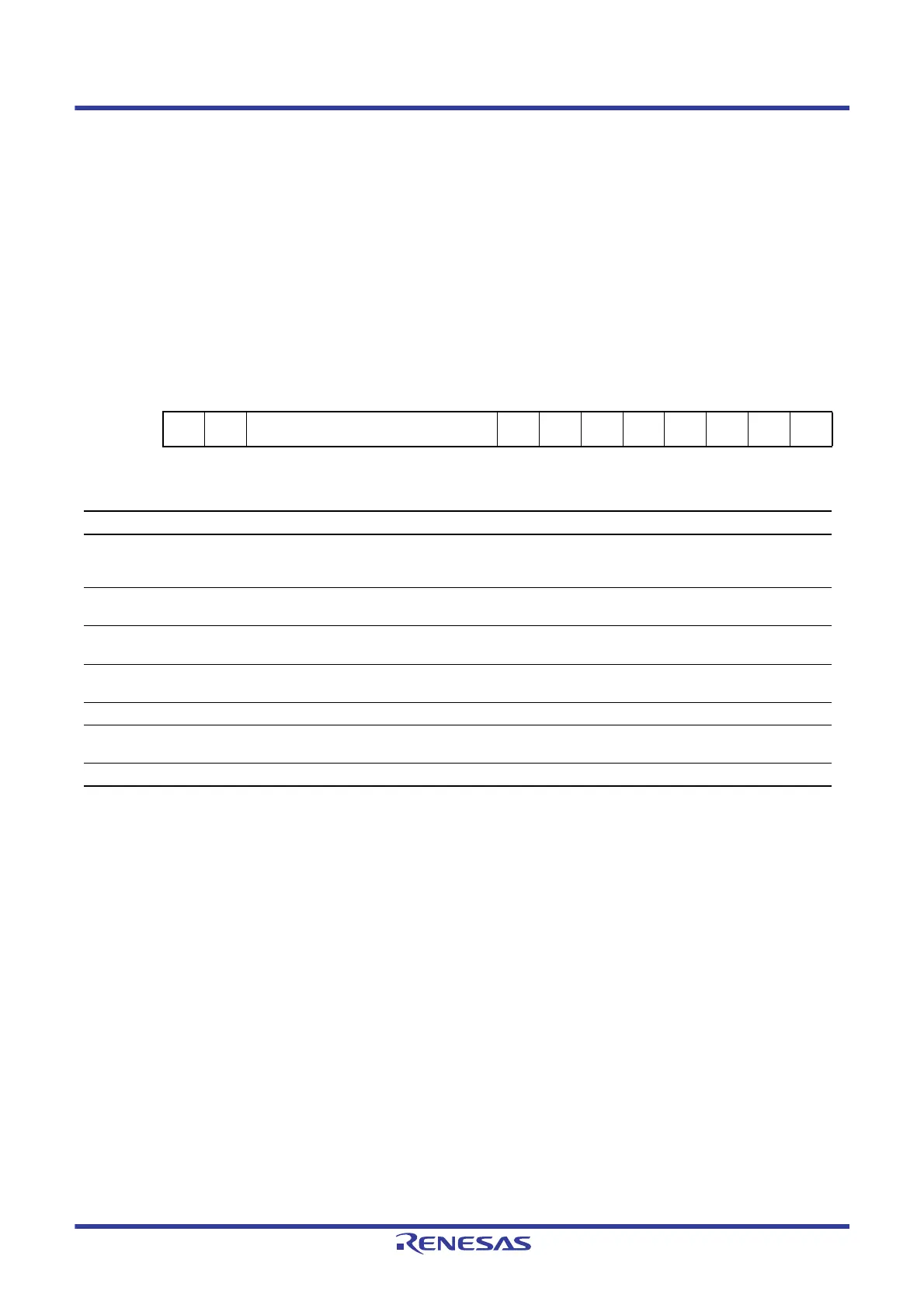

Address(es): RSCAN.RFSTS0 000A 8340h, RSCAN.RFSTS1 000A 8342h

b15 b14 b13 b12 b11 b10 b9 b8 b7 b6 b5 b4 b3 b2 b1 b0

—— RFMC[5:0] ————RFIFRFMLTRFFLLRFEMP

Value after reset:

0000000000000001

Bit Symbol Bit Name Description R/W

b0 RFEMP Receive FIFO Buffer Empty

Status Flag

0: The receive FIFO buffer contains unread messages.

1: The receive FIFO buffer contains no unread message

(buffer empty).

R

b1 RFFLL Receive FIFO Buffer Full

Status Flag

0: The receive FIFO buffer is not full.

1: The receive FIFO buffer is full.

R

b2 RFMLT Receive FIFO Message Lost

Flag

0: No receive FIFO message is lost.

1: A receive FIFO message is lost.

R/(W)

*

1

b3 RFIF Receive FIFO Interrupt

Request Flag

0: No receive FIFO interrupt request is present.

1: A receive FIFO interrupt request is present.

R/(W)

*

1

b7 to b4 — Reserved These bits are read as 0. The write value should be 0. R/W

b13 to b8 RFMC[5:0] Receive FIFO Unread

Message Counter

The number of unread messages stored in the receive FIFO

buffer is displayed.

R

b15, b14 — Reserved These bits are read as 0. The write value should be 0. R/W

Loading...

Loading...