R01UH0823EJ0100 Rev.1.00 Page 1233 of 1823

Jul 31, 2019

RX23W Group 36. CAN Module (RSCAN)

36.2.46 Transmit/Receive FIFO Control Register 0H (CFCCH0)

CFM[1:0] Bits (Transmit/Receive FIFO Mode Select)

These bits are used to select transmit/receive FIFO mode. Modify these bits only in global reset mode.

CFITSS Bit (Interval Timer Clock Source Select)

Setting this bit to 0 selects the clock selected by the CFITR bit as the clock source for counting by the interval timer.

Setting this bit to 1 selects the CAN bit time clock as the clock source for counting by the interval timer. Set the

CFCCL0.CFE bit to 0 (no transmit/receive FIFO buffer is used) before modifying the CFITSS bit.

CFITR Bit (Transmit/Receive FIFO Interval Timer Resolution)

This bit is valid when the setting of the CFITSS bit is 0.

Setting this bit to 0 selects the clock obtained by frequency-dividing PCLK by the GCFGH.ITRCP[15:0] value.

Setting this bit to 1 selects the clock obtained by frequency-dividing PCLK by the GCFGH.ITRCP[15:0] value × 10.

Modifying this bit with the CFCCL0.CFE bit set to 0 (no transmit/receive FIFO buffer is used).

CFTML[1:0] Bits (Transmit Buffer Link Configuration)

These bits are used to set the number of transmit buffer to be linked to the transmit/receive FIFO buffer when the

CFM[1:0] bits are set to 01b (transmit mode).

Setting the CFCCL0.CFDC[2:0] bits to 001b or more enables the setting of the CFTML[1:0] bits.

Modify these bits only in global reset mode.

CFITT[7:0] Bits (Message Transmission Interval Configuration)

These bits are used to set a message transmission interval when transmitting messages continuously from a transmit/

receive FIFO buffer whose CFM[1:0] bits are set to 01b (transmit mode).

Set the CFCCL0.CFE bit to 0 (no transmit/receive FIFO buffer is used) and then modify the CFITT[7:0] bits.

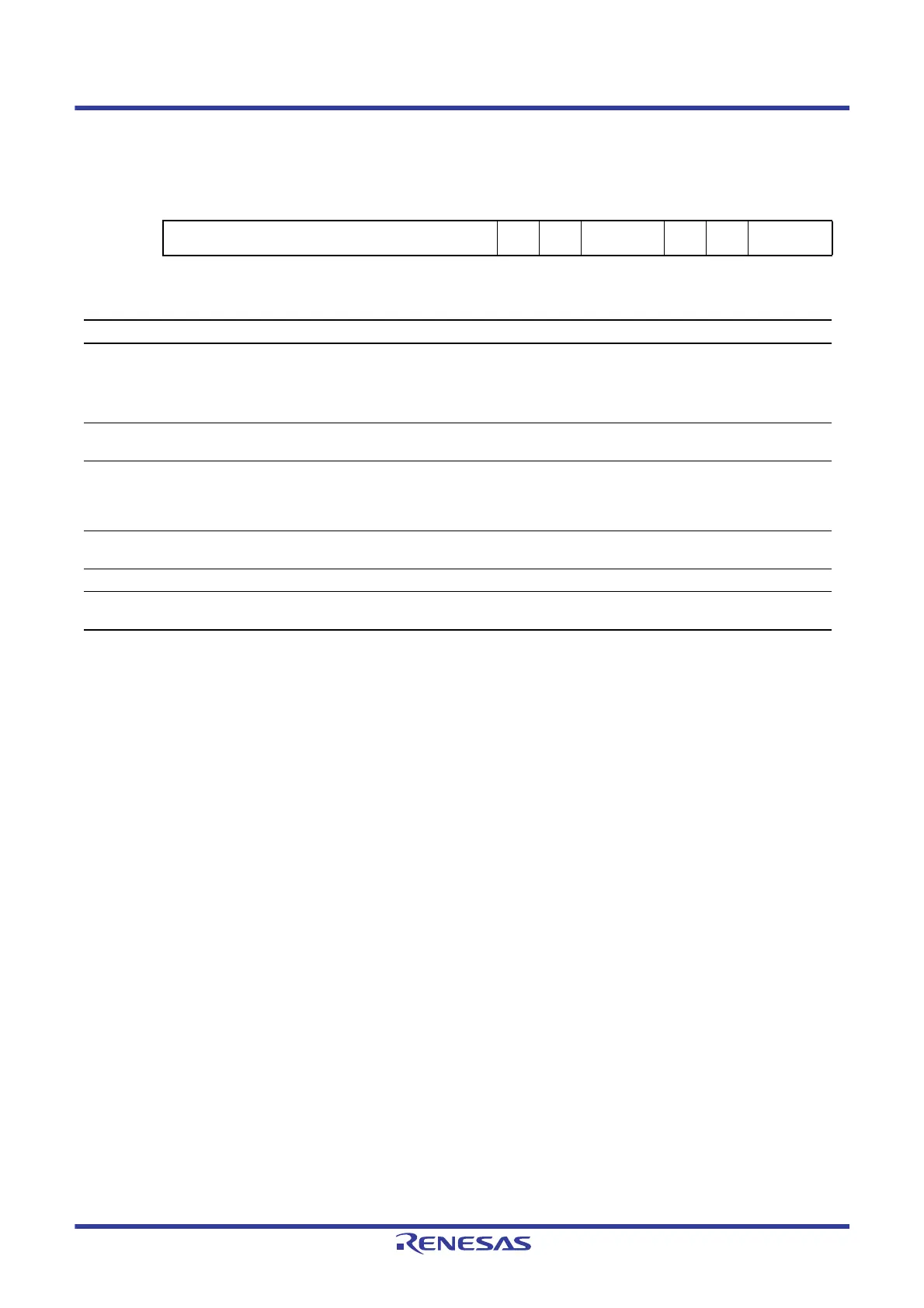

Address(es): RSCAN0.CFCCH0 000A 8352h

b15 b14 b13 b12 b11 b10 b9 b8 b7 b6 b5 b4 b3 b2 b1 b0

CFITT[7:0] — — CFTML[1:0] CFITR CFITSS CFM[1:0]

Value after reset:

0000000000000000

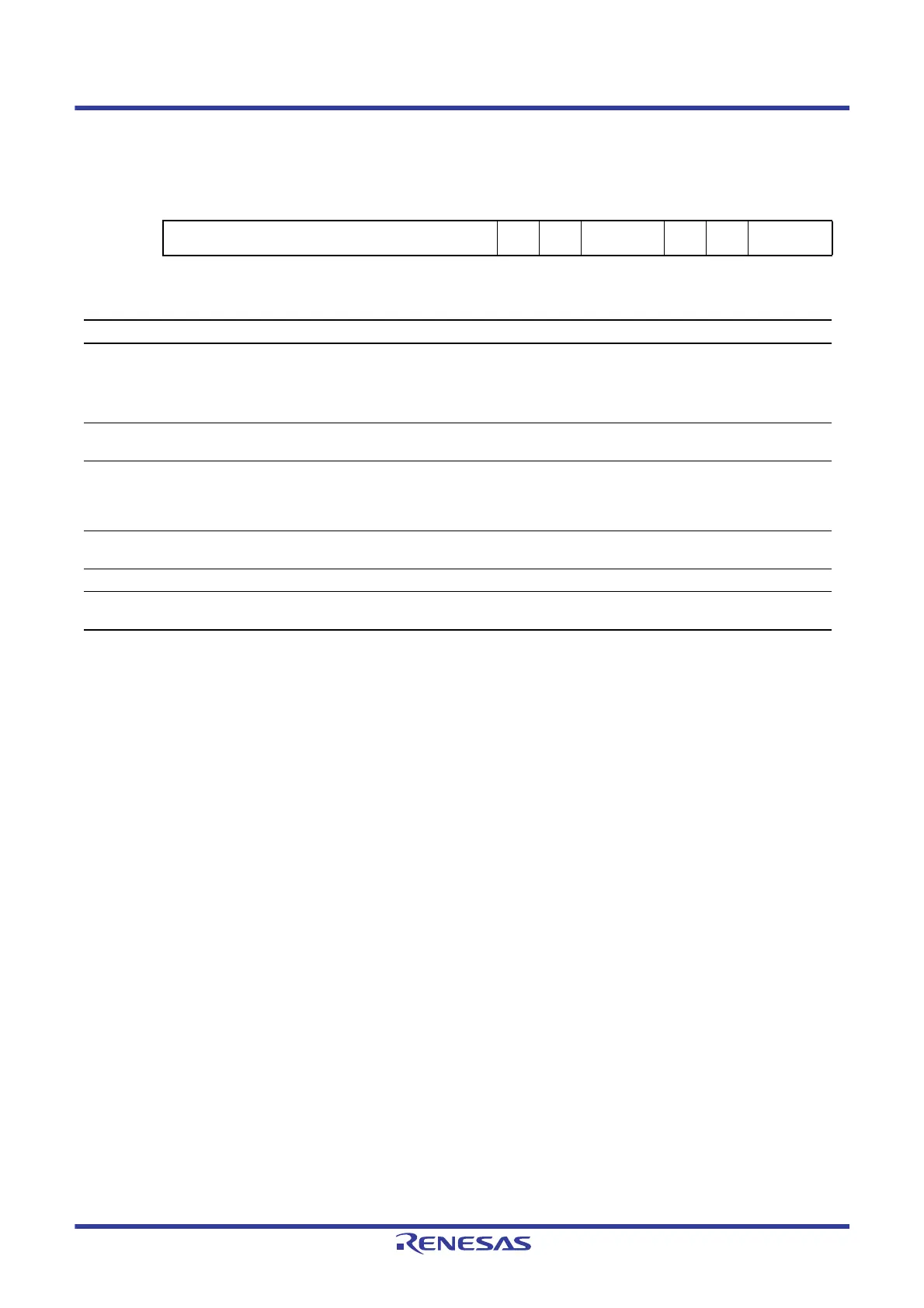

Bit Symbol Bit Name Description R/W

b1, b0 CFM[1:0] Transmit/Receive FIFO Mode

Select

b1 b0

0 0: Receive mode

0 1: Transmit mode

1 0: Setting prohibited

1 1: Setting prohibited

R/W

b2 CFITSS Interval Timer Clock Source

Select

0: Clock selected by the CFITR bit

1: CAN bit time clock

R/W

b3 CFITR Transmit/Receive FIFO Interval

Timer Resolution

0: Clock obtained by frequency-dividing PCLK by the

ITRCP[15:0] value

1: Clock obtained by frequency-dividing PCLK by the

ITRCP[15:0] value × 10

R/W

b5, b4 CFTML[1:0] Transmit Buffer Link

Configuration

Set the transmit buffer number to be linked to the transmit/

receive FIFO buffer.

R/W

b7, b6 — Reserved These bits are read as 0. The write value should be 0. R/W

b15 to b8 CFITT[7:0] Message Transmission Interval

Configuration

Set a message transmission interval.

Set these bits to a value within a range of 00h to FFh.

R/W

Loading...

Loading...