R01UH0823EJ0100 Rev.1.00 Page 232 of 1823

Jul 31, 2019

RX23W Group 11. Low Power Consumption

11.2.7 Sub Operating Power Control Register (SOPCCR)

Note: Set the PRCR.PRC1 bit to 1 (write enabled) before rewriting this register.

Note 1. Depends on the setting of OPCCR.OPCM[2:0].

The SOPCCR register is used to reduce power consumption in normal operating mode, sleep mode, and deep sleep mode

by controlling a transition to low-speed operating mode.

Setting this register initiates entry to/exit from low-speed operating mode.

Low-speed operating mode is used for the sub-clock oscillator only.

The OPCCR register cannot be rewritten when the SOPCM bit is 1 (low-speed operating mode).

The SOPCCR register cannot be rewritten under the following conditions:

When the SOPCCR.SOPCMTSF flag is 1 (during transition)

Time period from WAIT instruction execution for a sleep mode transition, until exit from sleep mode to normal

operation

Time period from WAIT instruction execution for a deep sleep mode transition, until exit from deep sleep mode to

normal operation

This register cannot be rewritten while the flash memory is being programmed or erased (P/E).

For the procedures for changing operating power control modes, refer to Function in

section 11.5, Function for Lower

Operating Power Consumption

.

During sleep mode or mode transitions, do not write to the registers related to system control (indicated by ‘SYSTEM’ in

the Module Symbol column in

Table 5.1, List of I/O Registers (Address Order)).

SOPCM Bit (Sub Operating Power Control Mode Select)

The SOPCM bit selects operating power control in normal operating mode and sleep mode.

Setting this bit to 1 allows a transition to low-speed operating mode. Setting this bit to 0 allows a return to the operating

mode (operating mode set by OPCCR.OPCM[2:0]) before the transition to low-speed operating mode.

Table 11.4 shows the relationship between operating power control modes, the OPCM[2:0] and SOPCM bit settings,

and the operating frequency and voltage ranges.

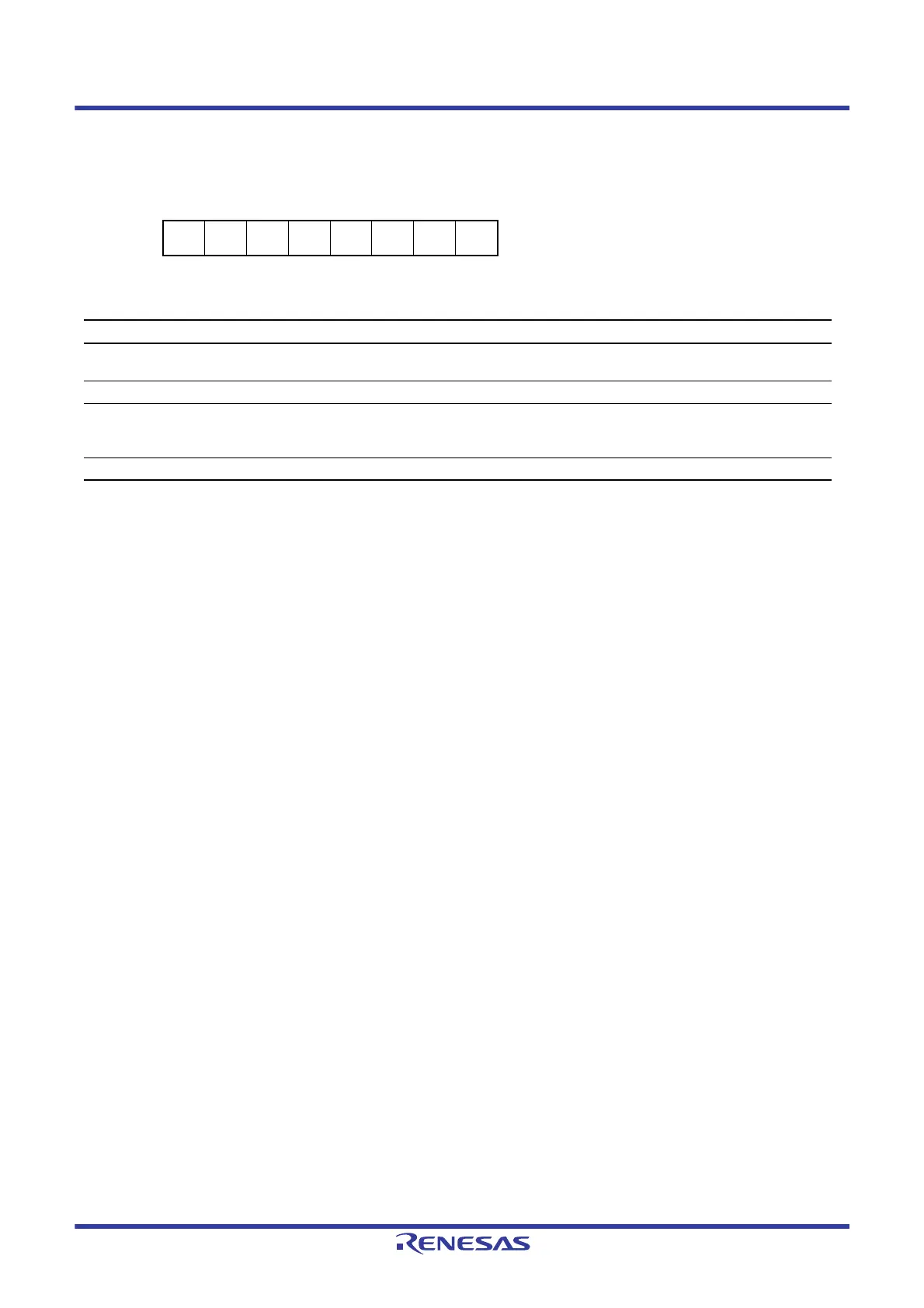

Address(es): 0008 00AAh

b7 b6 b5 b4 b3 b2 b1 b0

———

SOPC

MTSF

———

SOPC

M

Value after reset:

00000000

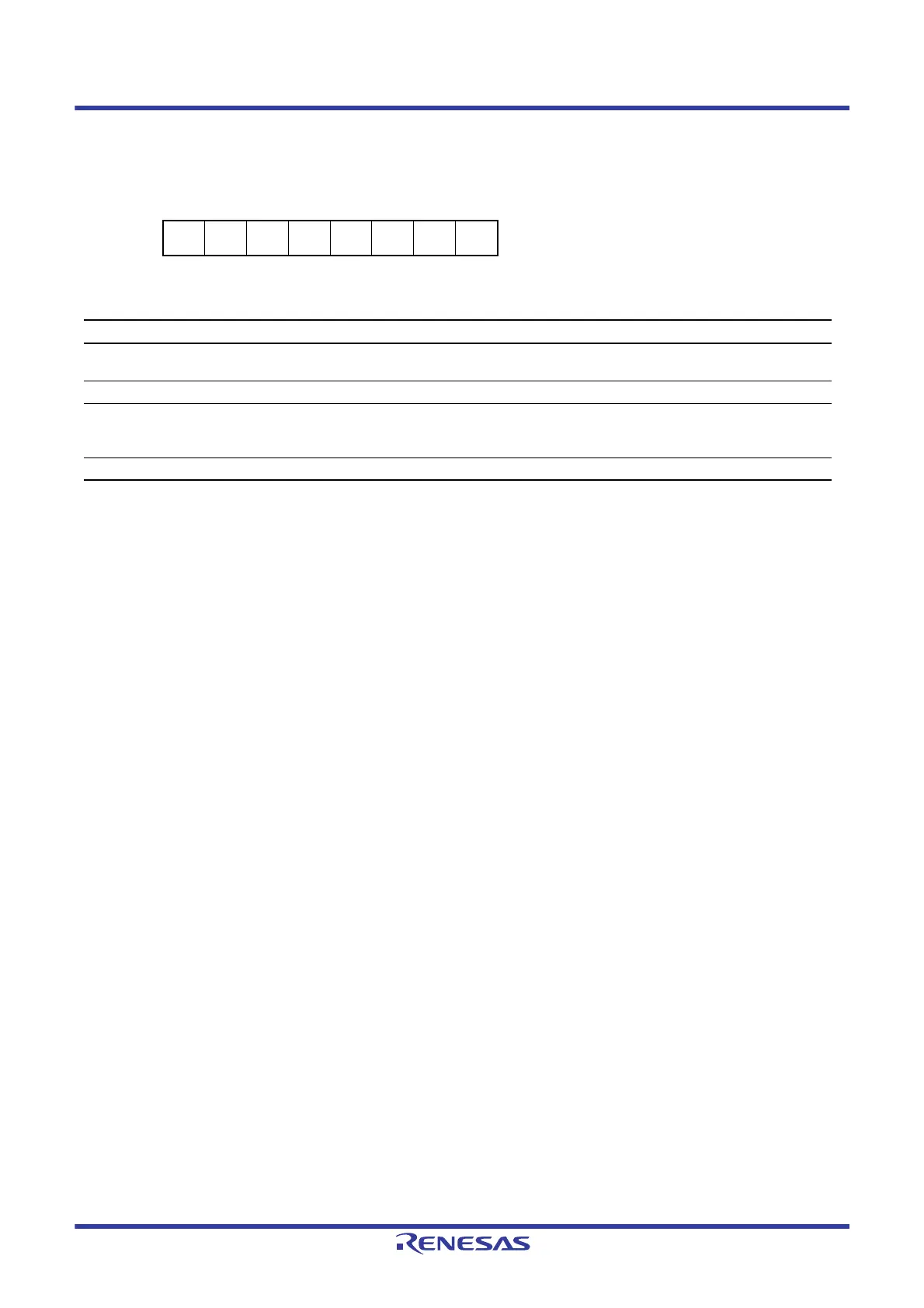

Bit Symbol Bit Name Description R/W

b0 SOPCM Sub Operating Power

Control Mode Select

0: High-speed operating mode or middle-speed operating mode*

1

1: Low-speed operating mode

R/W

b3 to b1 — Reserved These bits are read as 0. The write value should be 0. R/W

b4 SOPCMTSF Sub Operating Power

Control Mode Transition

Status Flag

0: Transition completed

1: During transition

R

b7 to b5 — Reserved These bits are read as 0. The write value should be 0. R/W

Loading...

Loading...