R01UH0823EJ0100 Rev.1.00 Page 149 of 1823

Jul 31, 2019

RX23W Group 7. Option-Setting Memory (OFSM)

7.2 Register Descriptions

7.2.1 Option Function Select Register 0 (OFS0)

Address(es): OFSM.OFS0 FFFF FF8Ch

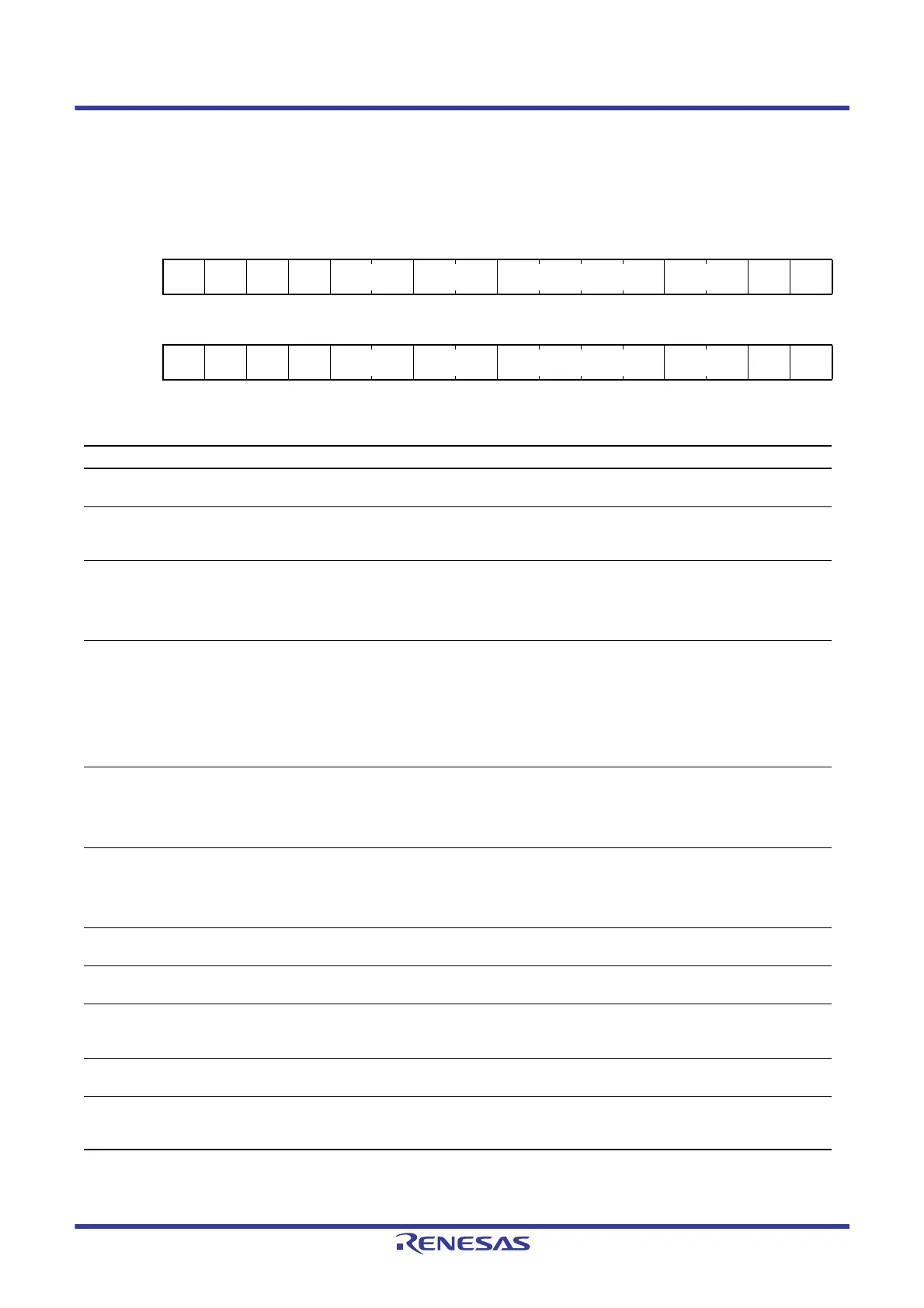

b31 b30 b29 b28 b27 b26 b25 b24 b23 b22 b21 b20 b19 b18 b17 b16

———

WDTRS

TIRQS

WDTRPSS[1:0] WDTRPES[1:0] WDTCKS[3:0] WDTTOPS[1:0]

WDTST

RT

—

Value after reset:

The value set by the user*

1

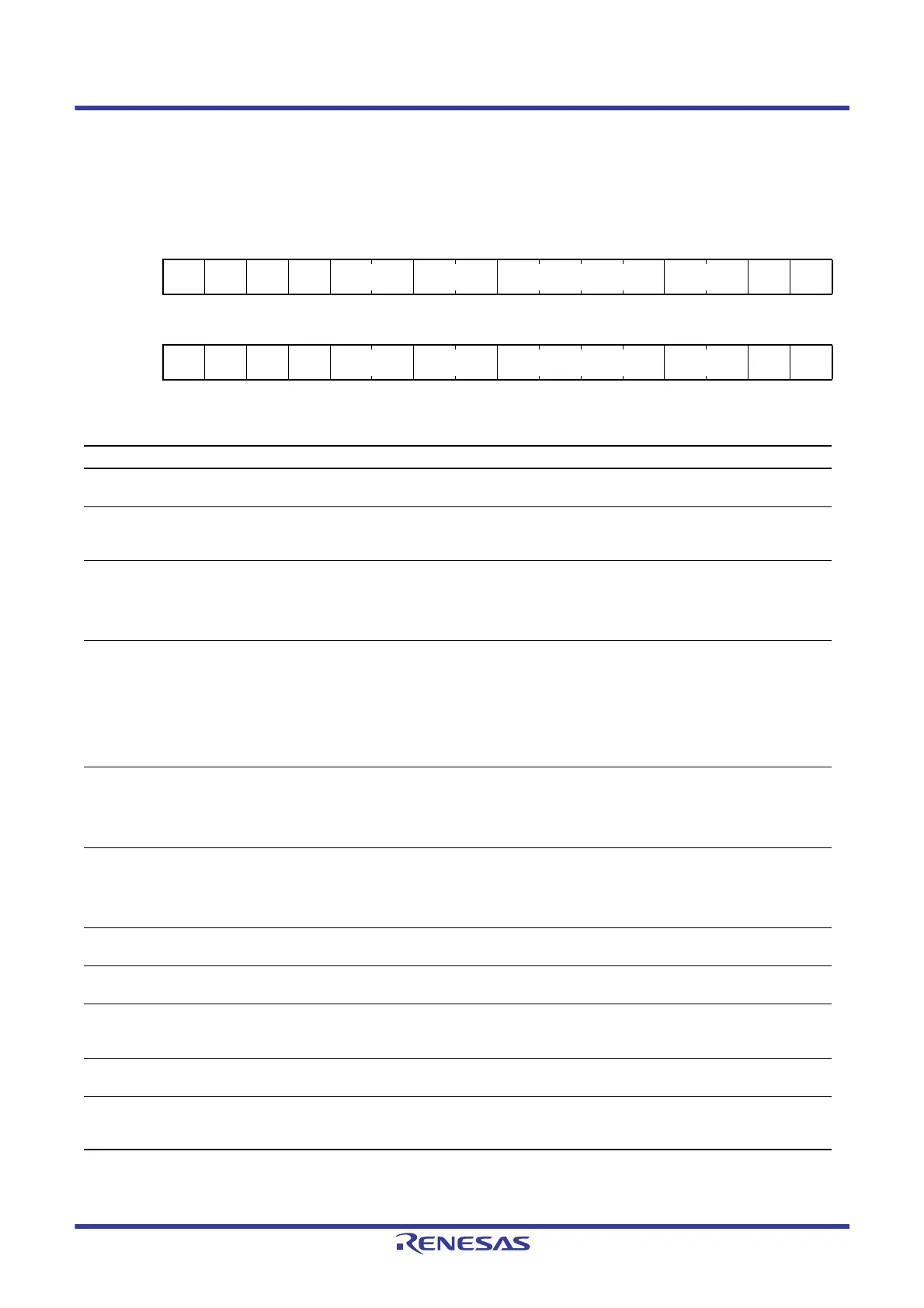

b15 b14 b13 b12 b11 b10 b9 b8 b7 b6 b5 b4 b3 b2 b1 b0

—

IWDTS

LCSTP

—

IWDTR

STIRQS

IWDTRPSS[1:0] IWDTRPES[1:0] IWDTCKS[3:0] IWDTTOPS[1:0]

IWDTS

TRT

—

Value after reset:

The value set by the user*

1

Bit Symbol Bit Name Description R/W

b0 — Reserved When reading, this bit returns the value written by the user.

The write value should be 1.

R

b1 IWDTSTRT IWDT Start Mode Select 0: IWDT is automatically activated in auto-start mode after a

reset

1: IWDT is halted after a reset

R

b3, b2 IWDTTOPS[1:0] IWDT Timeout Period Select

b3 b2

0 0: 128 cycles (007Fh)

0 1: 512 cycles (01FFh)

1 0: 1024 cycles (03FFh)

1 1: 2048 cycles (07FFh)

R

b7 to b4 IWDTCKS[3:0] IWDT Clock Frequency

Division Ratio Select

b7 b4

0 0 0 0: No division

0 0 1 0: Divide-by-16

0 0 1 1: Divide-by-32

0 1 0 0: Divide-by-64

1 1 1 1: Divide-by-128

0 1 0 1: Divide-by-256

Settings other than above are prohibited.

R

b9, b8 IWDTRPES[1:0] IWDT Window End Position

Select

b9 b8

0 0: 75%

0 1: 50%

1 0: 25%

1 1: 0% (No window end position setting)

R

b11, b10 IWDTRPSS[1:0] IWDT Window Start Position

Select

b11 b10

0 0: 25%

0 1: 50%

1 0: 75%

1 1: 100% (No window start position setting)

R

b12 IWDTRSTIRQS IWDT Reset Interrupt

Request Select

0: Non-maskable interrupt request is enabled

1: Reset is enabled

R

b13 — Reserved When reading, this bit returns the value written by the user.

The write value should be 1.

R

b14 IWDTSLCSTP IWDT Sleep Mode Count

Stop Control

0: Counting stop is disabled

1: Counting stop is enabled when entering sleep, software

standby, or deep sleep mode

R

b16, b15 — Reserved When reading, these bits return the value written by the

user. The write value should be 1.

R

b17 WDTSTRT WDT Start Mode Select 0: WDT is automatically activated in auto-start mode after a

reset

1: WDT is stopped after a reset

R

Loading...

Loading...