R01UH0823EJ0100 Rev.1.00 Page 1250 of 1823

Jul 31, 2019

RX23W Group 36. CAN Module (RSCAN)

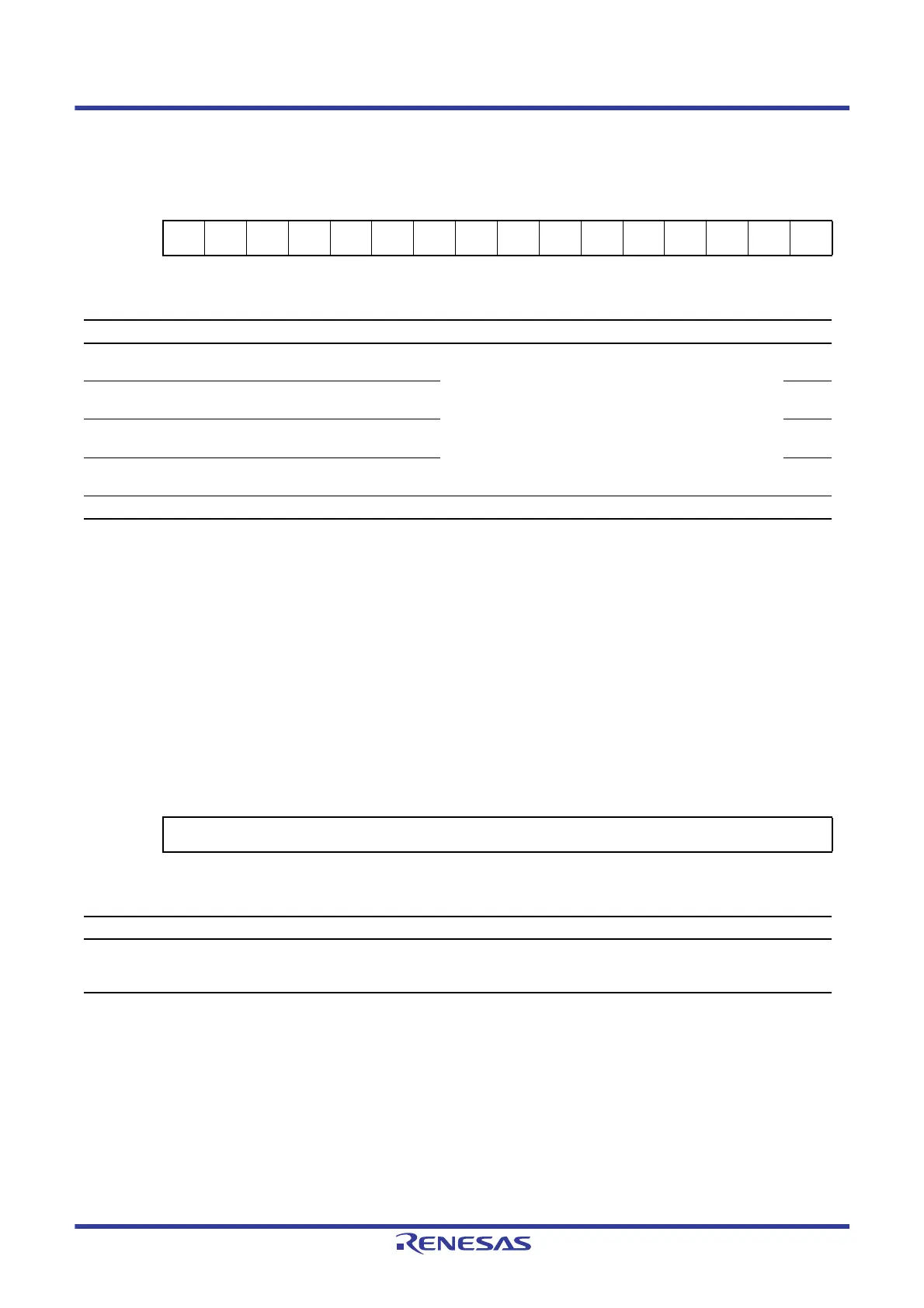

36.2.66 Transmit Buffer Interrupt Enable Register (TMIEC)

TMIEp Bit (RSCAN0 Transmit Buffer p Interrupt Enable) (p = 0 to 3)

When TMIEp bit is set to 1 and the corresponding transmission has been completed, a transmit buffer interrupt request is

generated.

Modify this bit when the corresponding TMSTSp.TMTRM flag is 0 (no transmit request is present).

Write 0 to bits corresponding to transmit buffers linked to transmit/receive FIFO buffers.

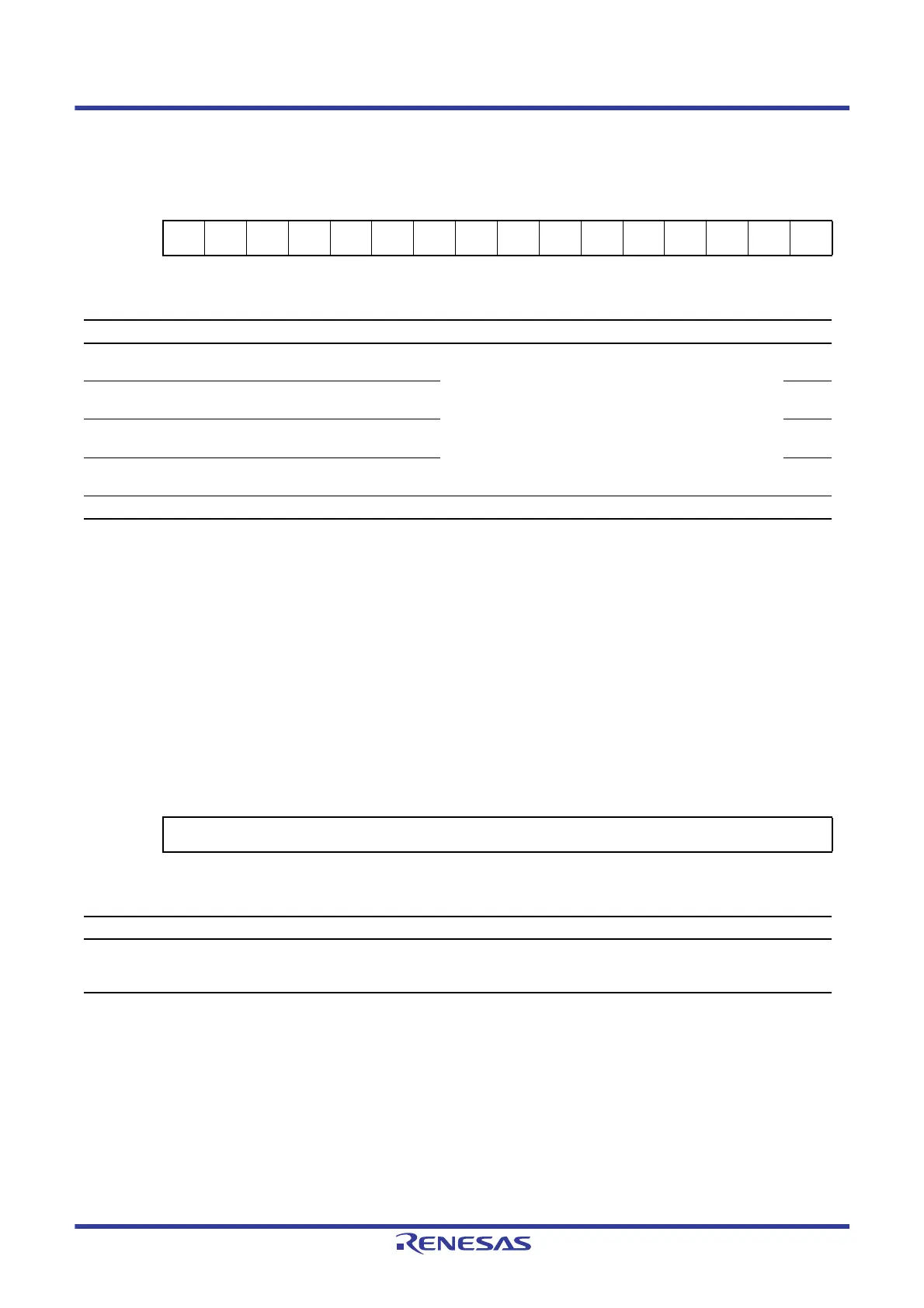

36.2.67 Transmit Buffer Register pAL (TMIDLp) (p = 0 to 3)

Modify this register when the corresponding TMSTSp.TMTRM flag is 0 (no transmit request is present). If this register

is linked to any transmit/receive FIFO buffer, do not write data to this register.

This register can be read/written when the GRWCR.RPAGE bit is 1.

TMID[15:0] Bits (Transmit Buffer ID Data L)

These bits are used to set the ID of the message to be transmitted from the transmit buffer.

Address(es): RSCAN0.TMIEC 000A 837Ah

b15 b14 b13 b12 b11 b10 b9 b8 b7 b6 b5 b4 b3 b2 b1 b0

————————————TMIE3TMIE2TMIE1TMIE0

Value after reset:

0000000000000000

Bit Symbol Bit Name Description R/W

b0 TMIE0 RSCAN0 Transmit Buffer 0

Interrupt Enable

0: Transmit buffer interrupt is disabled.

1: Transmit buffer interrupt is enabled.

R/W

b1 TMIE1 RSCAN0 Transmit Buffer 1

Interrupt Enable

R/W

b2 TMIE2 RSCAN0 Transmit Buffer 2

Interrupt Enable

R/W

b3 TMIE3 RSCAN0 Transmit Buffer 3

Interrupt Enable

R/W

b15 to b4 — Reserved These bits are read as 0. The write value should be 0. R/W

Address(es): RSCAN0.TMIDL0 000A 8600h, RSCAN0.TMIDL1 000A 8610h, RSCAN0.TMIDL2 000A 8620h,

RSCAN0.TMIDL3 000A 8630h

b15 b14 b13 b12 b11 b10 b9 b8 b7 b6 b5 b4 b3 b2 b1 b0

TMID[15:0]

Value after reset:

0000000000000000

Bit Symbol Bit Name Description R/W

b15 to b0 TMID[15:0] Transmit Buffer ID Data L Set standard ID or extended ID.

For standard ID, write an ID to b10 to b0 and write 0 to b15

to b11.

R/W

Loading...

Loading...