R01UH0823EJ0100 Rev.1.00 Page 822 of 1823

Jul 31, 2019

RX23W Group 30. Watchdog Timer (WDTA)

30.2.2 WDT Control Register (WDTCR)

There are some restrictions on writing to the WDTCR register. For details, refer to section 30.3.2, Control over

Writing to the WDTCR and WDTRCR Registers

.

In auto-start mode, the settings in the WDTCR register are disabled, and the settings in option function select register 0

(OFS0) are enabled. The bit setting made to the WDTCR register can also be made in OFS0 register. For details, refer to

section 30.3.7, Correspondence between Option Function Select Register 0 (OFS0) and WDT Registers.

TOPS[1:0] Bits (Timeout Period Selection)

These bits select the timeout period (period until the down-counter underflows) from among 1024, 4096, 8192, and

16384 cycles, taking the divided clock specified by the CKS[3:0] bits as one cycle.

After the down-counter is refreshed, the combination of the CKS[3:0] and TOPS[1:0] bits determines the time (number

of PCLK cycles) until the counter underflows.

Relations between the CKS[3:0] and TOPS[1:0] bit settings, the timeout period, and the number of PCLK cycles are

listed in

Table 30.2.

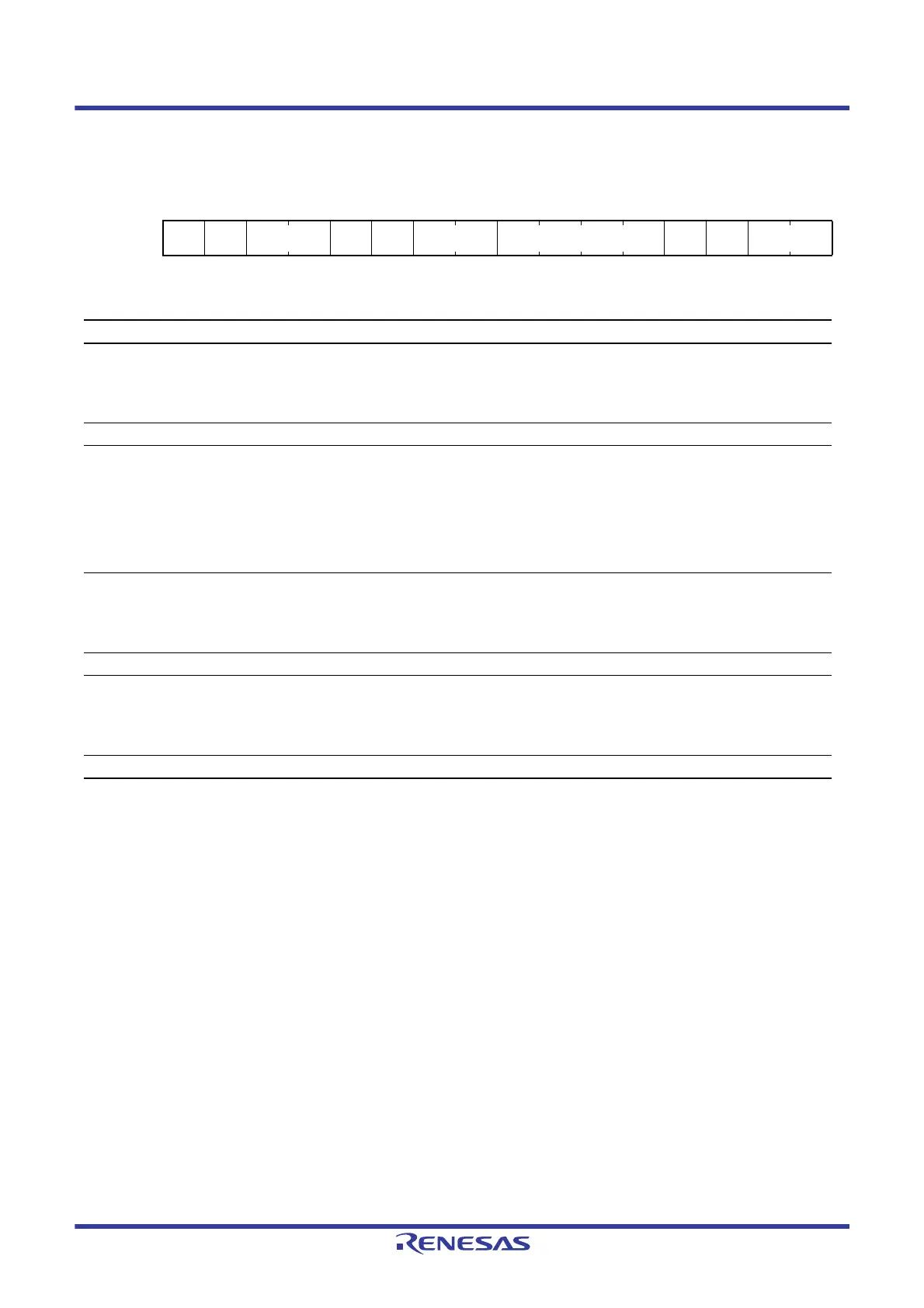

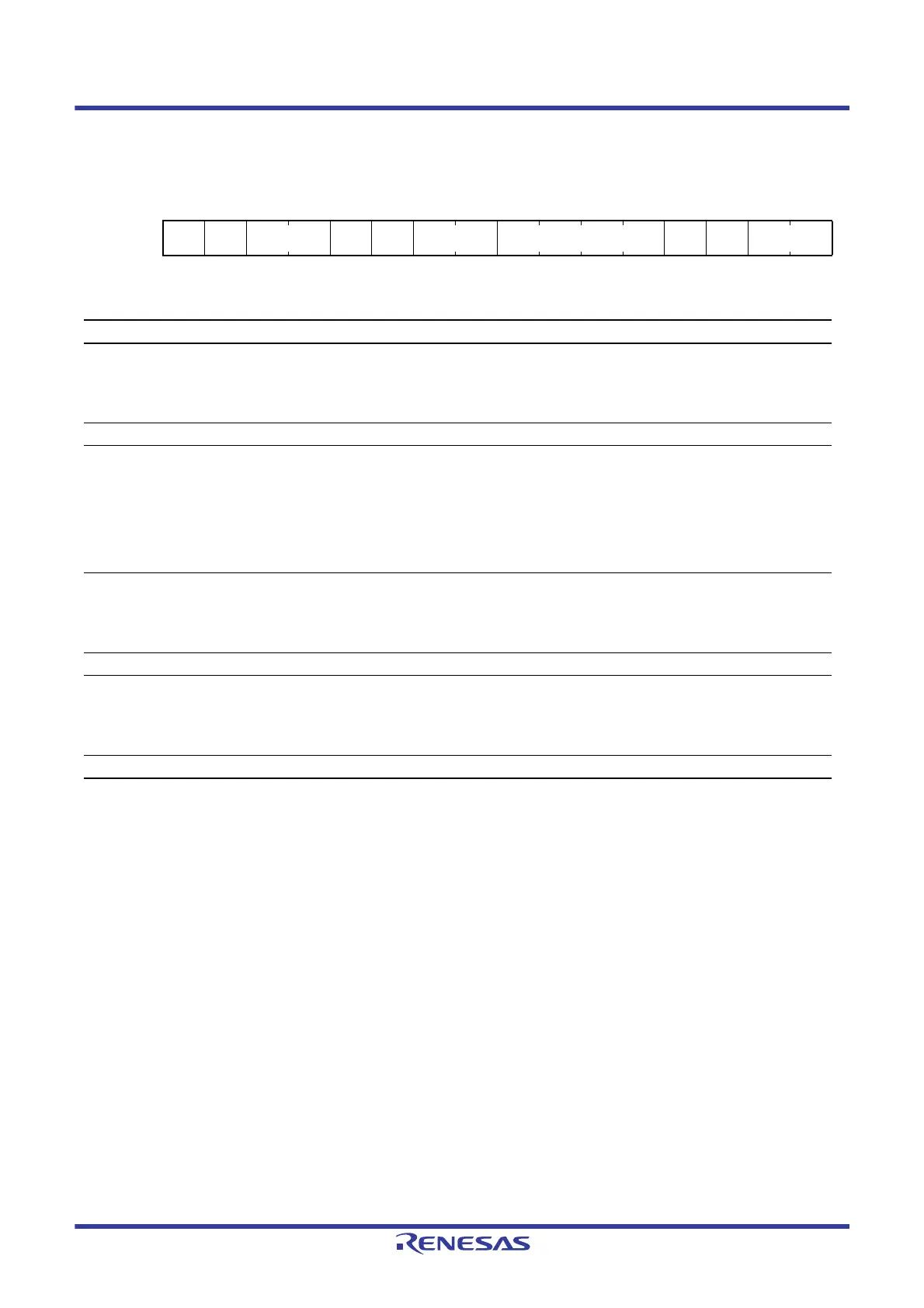

Address(es): 0008 8022h

b15 b14 b13 b12 b11 b10 b9 b8 b7 b6 b5 b4 b3 b2 b1 b0

— — RPSS[1:0] — — RPES[1:0] CKS[3:0] — — TOPS[1:0]

Value after reset:

0011001111110011

Bit Symbol Bit Name Description R/W

b1, b0 TOPS[1:0] Timeout Period Selection

b1 b0

0 0: 1024 cycles (03FFh)

0 1: 4096 cycles (0FFFh)

1 0: 8192 cycles (1FFFh)

1 1: 16384 cycles (3FFFh)

R/W

b3, b2 — Reserved These bits are read as 0 and cannot be modified. R

b7 to b4 CKS[3:0] Clock Division Ratio Selection

b7 b4

0 0 0 1: Divide-by-4

0 1 0 0: Divide-by-64

1 1 1 1: Divide-by-128

0 1 1 0: Divide-by-512

0 1 1 1: Divide-by-2048

1 0 0 0: Divide-by-8192

Setting other than above are prohibited.

R/W

b9, b8 RPES[1:0] Window End Position Selection

b9 b8

0 0: 75%

0 1: 50%

1 0: 25%

1 1: 0% (window end position is not specified)

R/W

b11, b10

— Reserved These bits are read as 0 and cannot be modified. R

b13, b12

RPSS[1:0] Window Start Position Selection

b13 b12

0 0: 25%

0 1: 50%

1 0: 75%

1 1: 100% (window start position is not specified)

R/W

b15, b14

— Reserved These bits are read as 0 and cannot be modified. R

Loading...

Loading...