R01UH0823EJ0100 Rev.1.00 Page 823 of 1823

Jul 31, 2019

RX23W Group 30. Watchdog Timer (WDTA)

CKS[3:0] Bits (Clock Division Ratio Selection)

These bits specify the division ration of the clock used for the down-counter. The division ration can be selected from

among the peripheral module clock (PCLK) divided by 4, 64, 128, 512, 2048, and 8192. Combined with the TOPS[1:0]

bit setting, a count period between 4,096 and 134,217,728 cycles of the PCLK clock can be selected for the WDT.

RPES[1:0] Bits (Window End Position Selection)

These bits specify the window end position that indicates the refresh-permitted period. 75%, 50%, 25%, or 0% of the

timeout period can be selected for the window end position. The selected window end position should be a value smaller

than the window start position (window start position > window end position). If the window end position is greater than

the window start position, only the window start position setting is enabled.

RPSS[1:0] Bits (Window Start Position Selection)

These bits specify the window start position that indicates the refresh-permitted period. 25%, 50%, 75%, or 100% of the

timeout period can be selected for the window end position. The window start position should be set to a value greater

the window end position. If the window start position is set to a value smaller than or equal to the window end position,

the window end position is set to 0%.

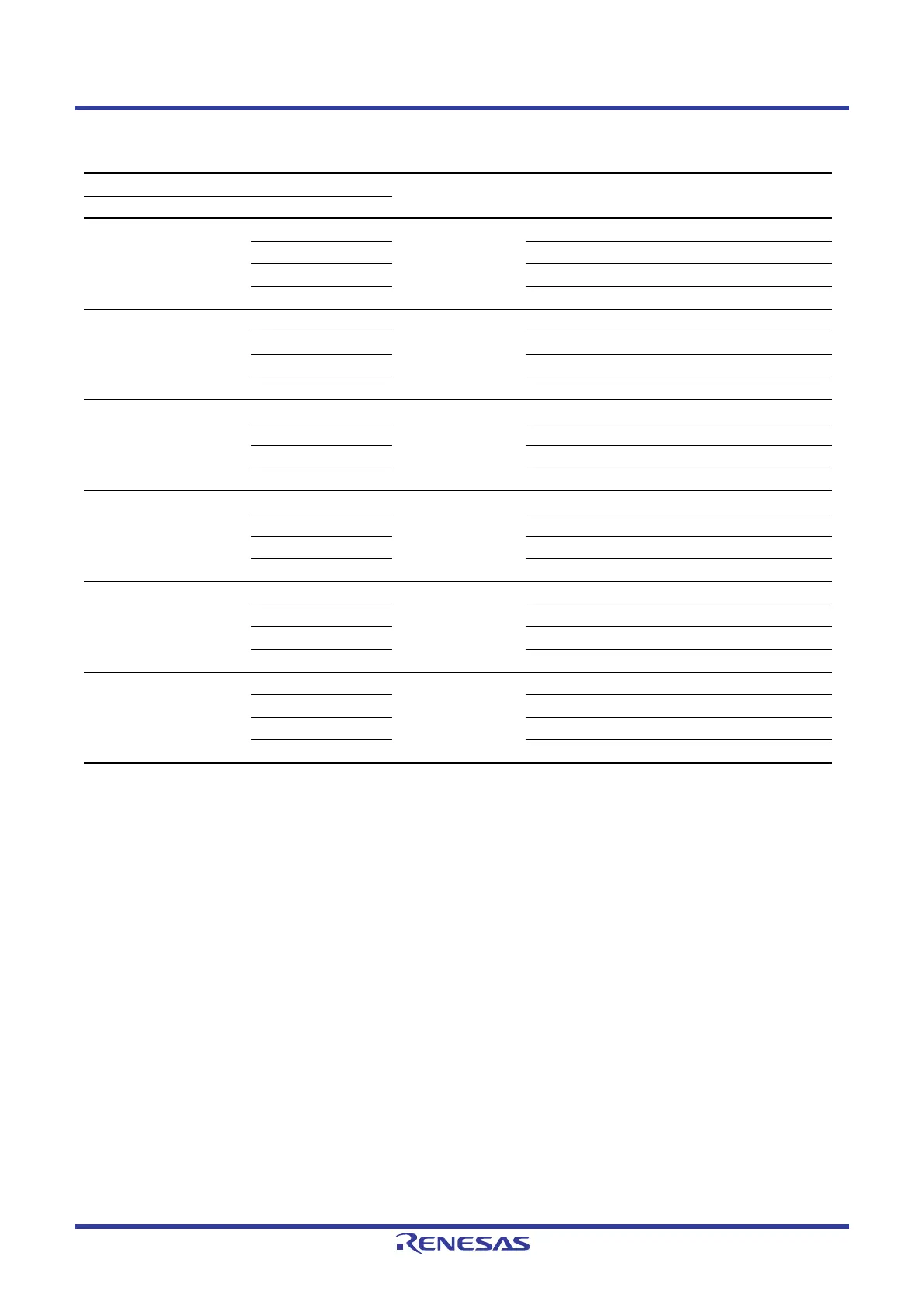

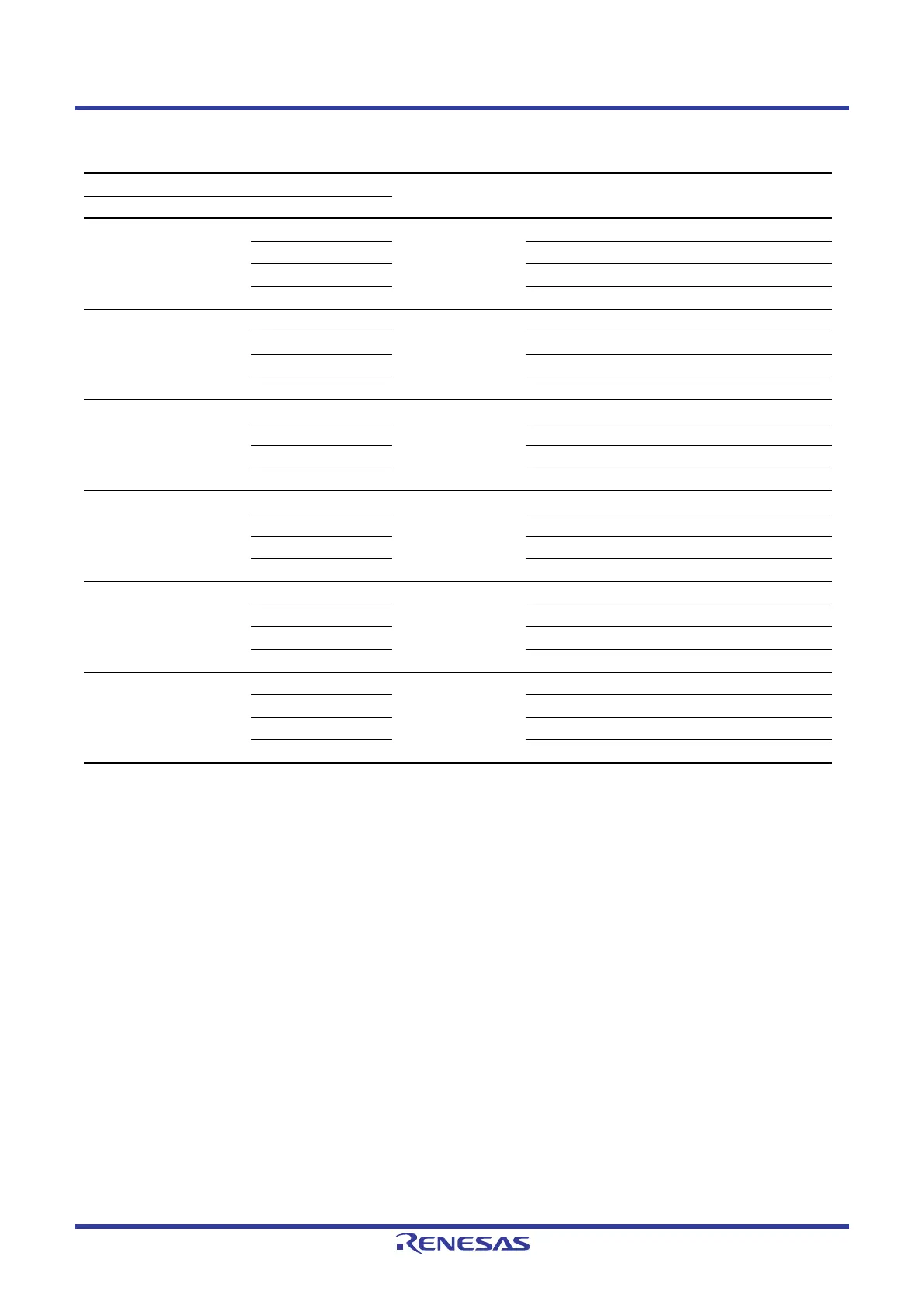

Table 30.2 Timeout Period Settings

CKS[3:0] Bits TOPS[1:0] Bits

Clock Division Ratio

Timeout Period

(Number of Cycles) Cycles of PCLK Clockb7 b6 b5 b4 b1 b0

0 0 0 1 0 0 Divide-by-4 1024 4096

0 1 4096 16384

1 0 8192 32768

1 1 16384 65536

0 1 0 0 0 0 Divide-by-64 1024 65536

0 1 4096 262144

1 0 8192 524288

1 1 16384 1048576

1 1 1 1 0 0 Divide-by-128 1024 131072

0 1 4096 524288

1 0 8192 1048576

1 1 16384 2097152

0 1 1 0 0 0 Divide-by-512 1024 524288

0 1 4096 2097152

1 0 8192 4194304

1 1 16384 8388608

0 1 1 1 0 0 Divide-by-2048 1024 2097152

0 1 4096 8388608

1 0 8192 16777216

1 1 16384 33554432

1 0 0 0 0 0 Divide-by-8192 1024 8388608

0 1 4096 33554432

1 0 8192 67108864

1 1 16384 134217728

Loading...

Loading...