R01UH0823EJ0100 Rev.1.00 Page 681 of 1823

Jul 31, 2019

RX23W Group 25. 16-Bit Timer Pulse Unit (TPUa)

25.2.10 Noise Filter Control Register (NFCR)

Note 1. These bits are reserved in TPU0, TPU1, TPU2, TPU4, and TPU5. The bits are read as 0. Writing to these bits is not possible.

Note 2. These bits are reserved in TPU0, TPU1, TPU2, and TPU5. The bits are read as 0. Writing to these bits is not possible.

Only set the TPUm.NFCR registers while the TPUm.TCNT is stopped.

NFAEN Bit (Noise Filter Enable A)

This bit disables or enables the noise filter for the TIOCAm pin (m = 3, 4).

Since unexpected edges may be internally generated when the value of NFAEN is changed, select the output compare

function in the timer I/O control register before changing the NFAEN value.

NFBEN Bit (Noise Filter Enable B)

This bit disables or enables the noise filter for the TIOCBm pin (m = 0 to 5).

Since unexpected edges may be internally generated when the value of NFBEN is changed, select the output compare

function in the timer I/O control register before changing the NFBEN value.

NFCEN Bit (Noise Filter Enable C)

This bit disables or enables the noise filter for the TIOCCm pin (m = 3).

Since unexpected edges may be internally generated when the value of NFCEN is changed, select the output compare

function in the timer I/O control register before changing the NFCEN value.

Address(es): TPU0.NFCR 0008 8108h, TPU1.NFCR 0008 8109h, TPU2.NFCR 0008 810Ah,

TPU3.NFCR 0008 810Bh, TPU4.NFCR 0008 810Ch, TPU5.NFCR 0008 810Dh

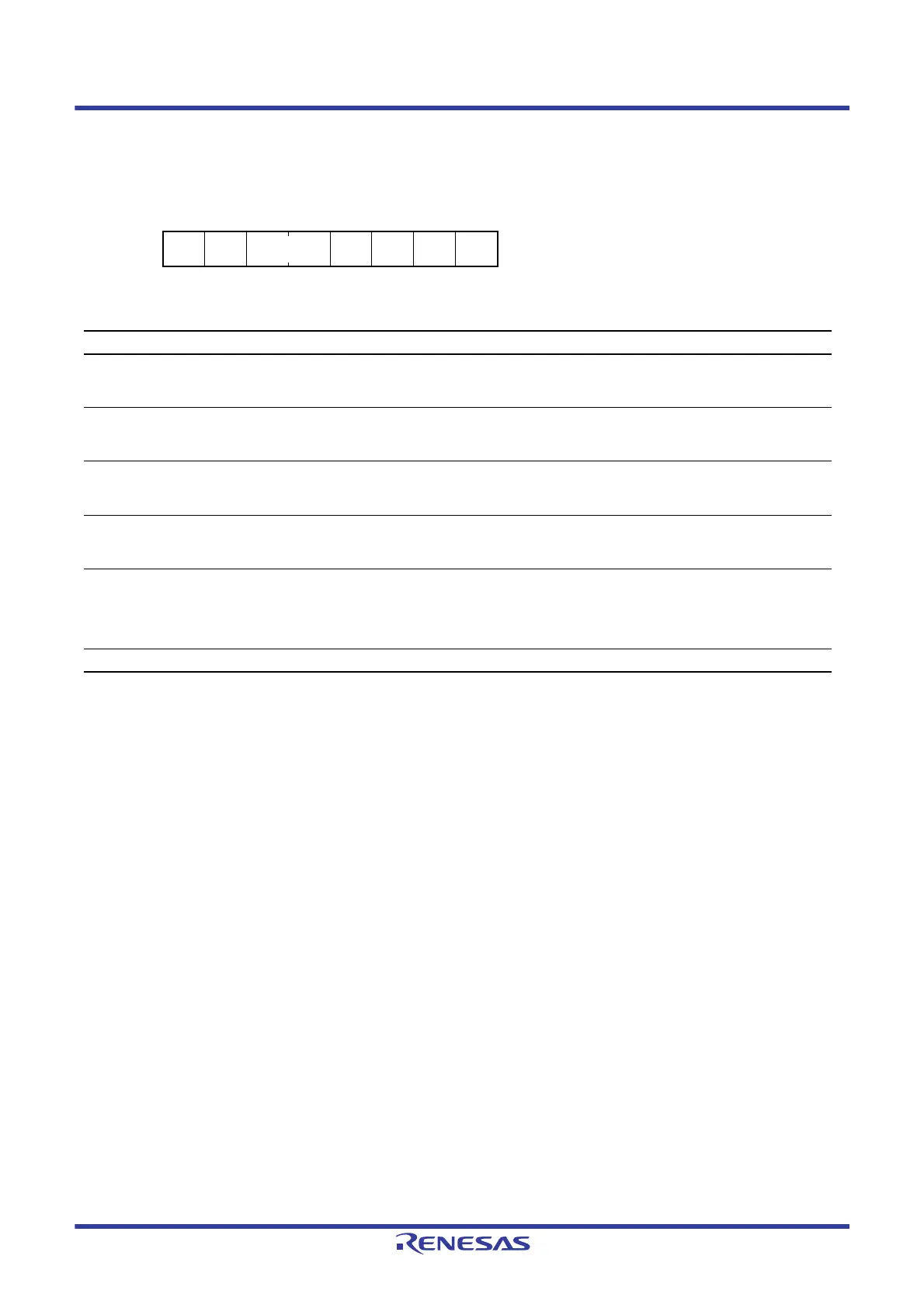

b7 b6 b5 b4 b3 b2 b1 b0

— — NFCS[1:0] NFDEN NFCEN NFBEN NFAEN

Value after reset:

00000000

Bit Symbol Bit Name Description R/W

b0 NFAEN Noise Filter Enable A*

2

0: The noise filter for TIOCAm is disabled.

1: The noise filter for TIOCAm is enabled.

(m = 3, 4)

R/W

b1 NFBEN Noise Filter Enable B 0: The noise filter for TIOCBm is disabled.

1: The noise filter for TIOCBm is enabled.

(m = 0 to 5)

R/W

b2 NFCEN Noise Filter Enable C*

1

0: The noise filter for TIOCCm is disabled.

1: The noise filter for TIOCCm is enabled.

(m = 3)

R/W

b3 NFDEN Noise Filter Enable D*

1

0: The noise filter for TIOCDm is disabled.

1: The noise filter for TIOCDm is enabled.

(m = 3)

R/W

b5, b4 NFCS[1:0] Noise Filter Clock Select

b5 b4

0 0: PCLK/1

0 1: PCLK/8

1 0: PCLK/32

1 1: Clock source that drives counting

R/W

b7, b6 — Reserved These bits are read as 0. Writing to these bits is not possible. R

Loading...

Loading...