R01UH0823EJ0100 Rev.1.00 Page 87 of 1823

Jul 31, 2019

RX23W Group 2. CPU

2.5.4 Data Arrangement

2.5.4.1 Data Arrangement in Registers

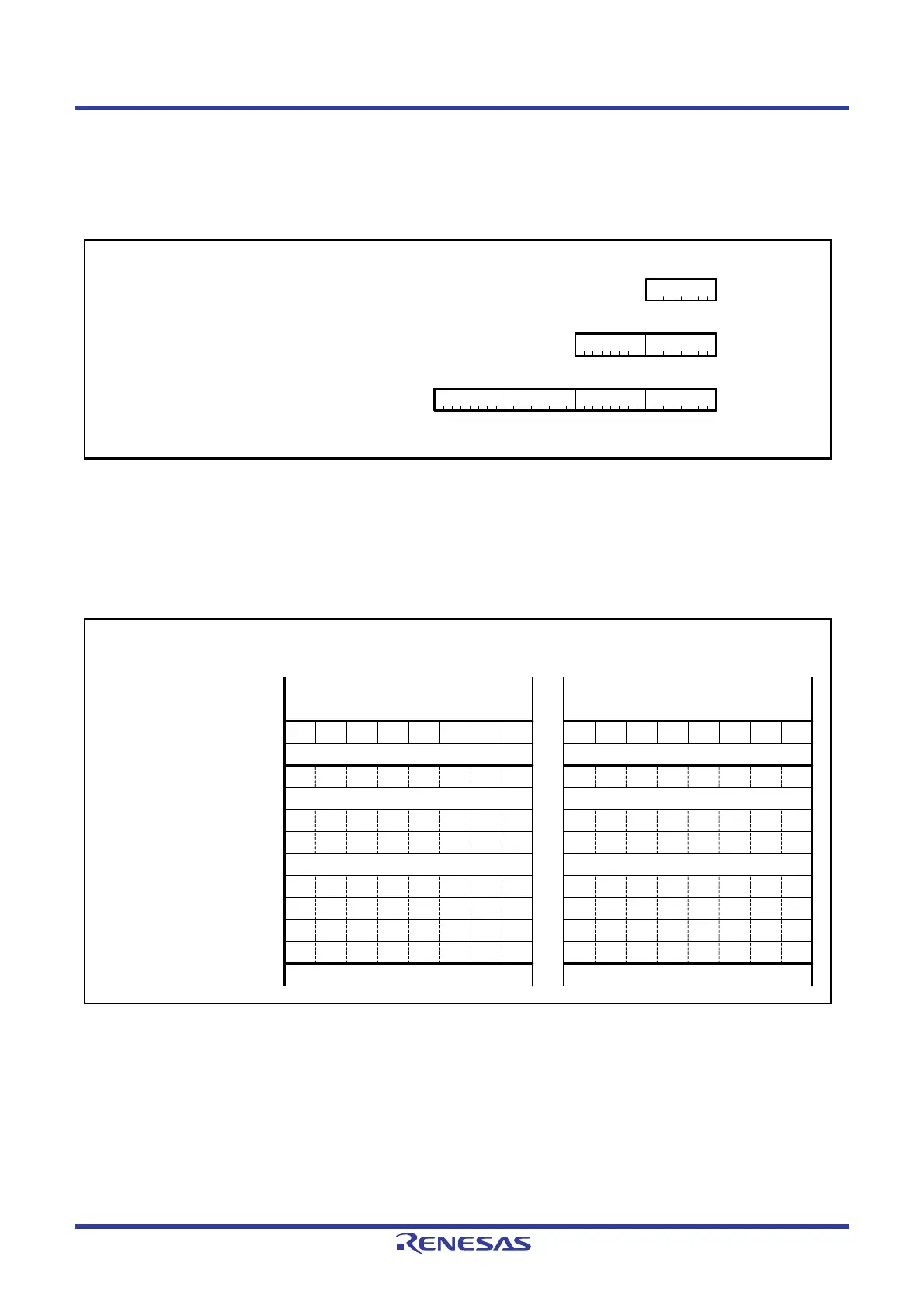

Figure 2.6 shows the relation between the sizes of registers and bit numbers.

Figure 2.6 Data Arrangement in Registers

2.5.4.2 Data Arrangement in Memory

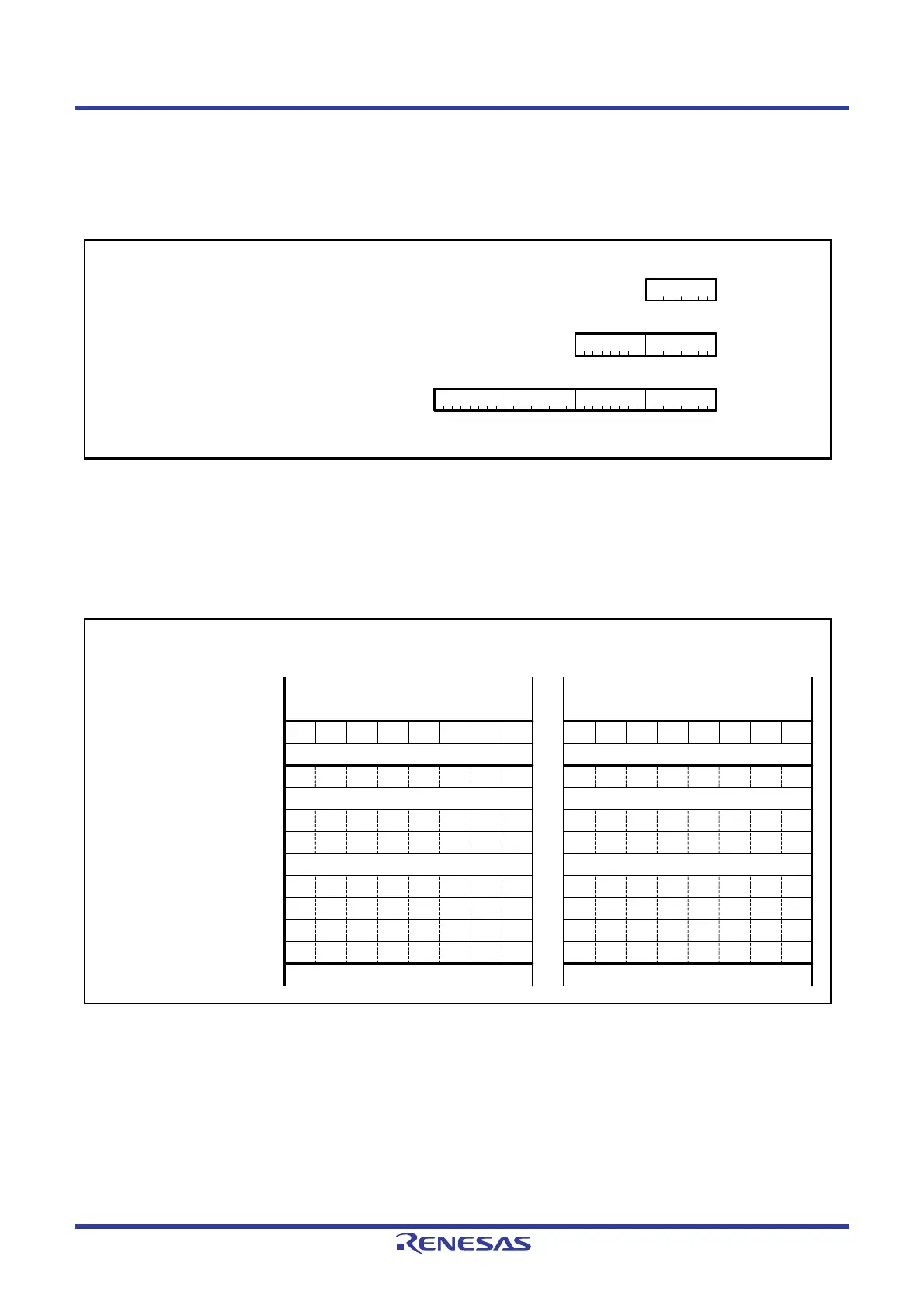

Data in memory have three sizes: byte (8-bit), word (16-bit), and longword (32-bit). The data arrangement is selectable

as little endian or big endian.

Figure 2.7 shows the arrangement of data in memory.

Figure 2.7 Data Arrangement in Memory

2.5.5 Notes on the Allocation of Instruction Codes

The allocation of instruction codes to an external space where the endian differs from that of the chip is prohibited. If the

instruction codes are allocated to the external space, they must be allocated to areas where the endian setting is the same

as that for the chip.

Longword (32-bit) data

b31 b0

b15 b0

b7 b0

Word (16-bit) data

Byte (8-bit) data

MSB LSB

1-bit data

(Little endian) (Big endian)

Address L

Address L

Byte data

Word data

Address M

Address M + 1

Address N

Address N + 1

Address N + 2

Address N + 3

Longword data

Data imageData type

b7

b0

LSBMSB

Data image

Address

7 6 5 4 3 2 1 0

LSB

LSB

MSB

MSB

b7

b0

LSBMSB

7 6 5 4 3 2 1 0

LSB

LSB

MSB

MSB

Loading...

Loading...