R01UH0823EJ0100 Rev.1.00 Page 276 of 1823

Jul 31, 2019

RX23W Group 15. Interrupt Controller (ICUb)

15.2.7 DMAC Trigger Select Register m (DMRSRm) (m = DMAC channel number)

To specify the same interrupt source for multiple DMRSRm registers is disabled. The interrupt source that has been

selected for the DMRSRm trigger should not be specified as the DTC trigger. Otherwise, the correct operation is not

guaranteed.

DMRS[7:0] Bits (DMAC Trigger Select)

The vector number of the interrupt source used as the DMAC trigger is specified in 8 bits. Do not set the vector numbers

that are not assigned for the DMAC trigger.

For the correspondence between interrupt sources and interrupt vector numbers, see

Table 15.3, Interrupt Vector

Tabl e

.

Write to the DMRSRm register while the DMA transfer enable bit of the DMA transfer enable register

(DMACm.DMCNT.DTE) is cleared to 0.

Address(es): ICU.DMRSR0 0008 7400h, ICU.DMRSR1 0008 7404h, ICU.DMRSR2 0008 7408h, ICU.DMRSR3 0008 740Ch

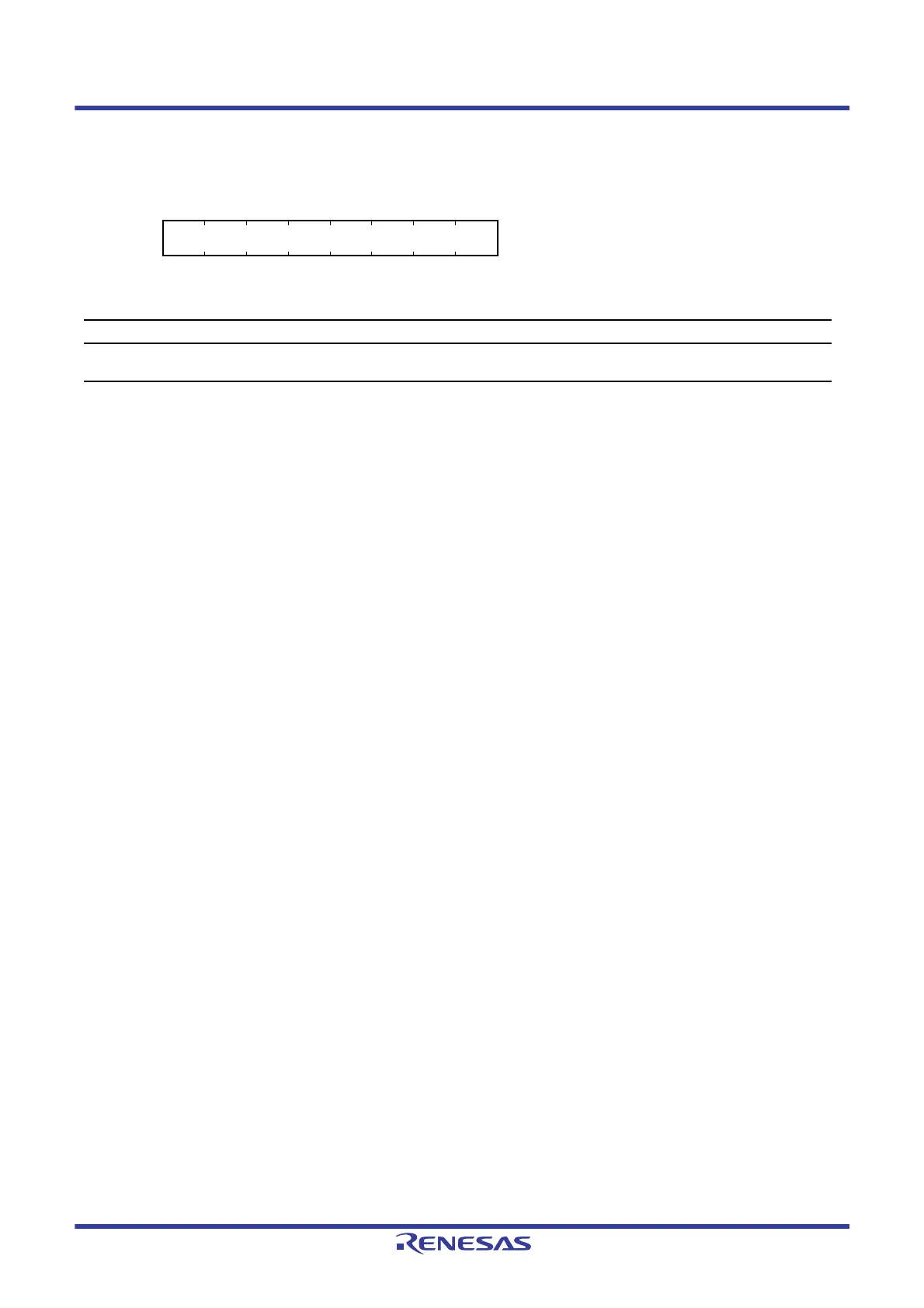

b7 b6 b5 b4 b3 b2 b1 b0

DMRS[7:0]

Value after reset:

00000000

Bit Symbol Bit Name Description R/W

b7 to b0 DMRS[7:0] DMAC Trigger Select These bits specify the vector number for the DMA transfer

request.

R/W

Loading...

Loading...