R01UH0823EJ0100 Rev.1.00 Page 340 of 1823

Jul 31, 2019

RX23W Group 18. DMA Controller (DMACA)

18.2 Register Descriptions

18.2.1 DMA Source Address Register (DMSAR)

Set DMSAR while DMAC activation is disabled (the DMST bit in DMAST = 0) or DMA transfer is disabled (the DTE

bit in DMCNT = 0).

Setting bits 31 to 29 is invalid; a value of bit 28 is extended to bits 31 to 29. Reading DMSAR returns the extended value.

18.2.2 DMA Destination Address Register (DMDAR)

DMDAR specifies the start address of the transfer destination. Set DMDAR while DMAC activation is disabled (the

DMST bit in DMAST = 0) or DMA transfer is disabled (the DTE bit in DMCNT = 0).

Setting bits 31 to 29 is invalid; a value of bit 28 is extended to bits 31 to 29. Reading DMDAR returns the extended

value.

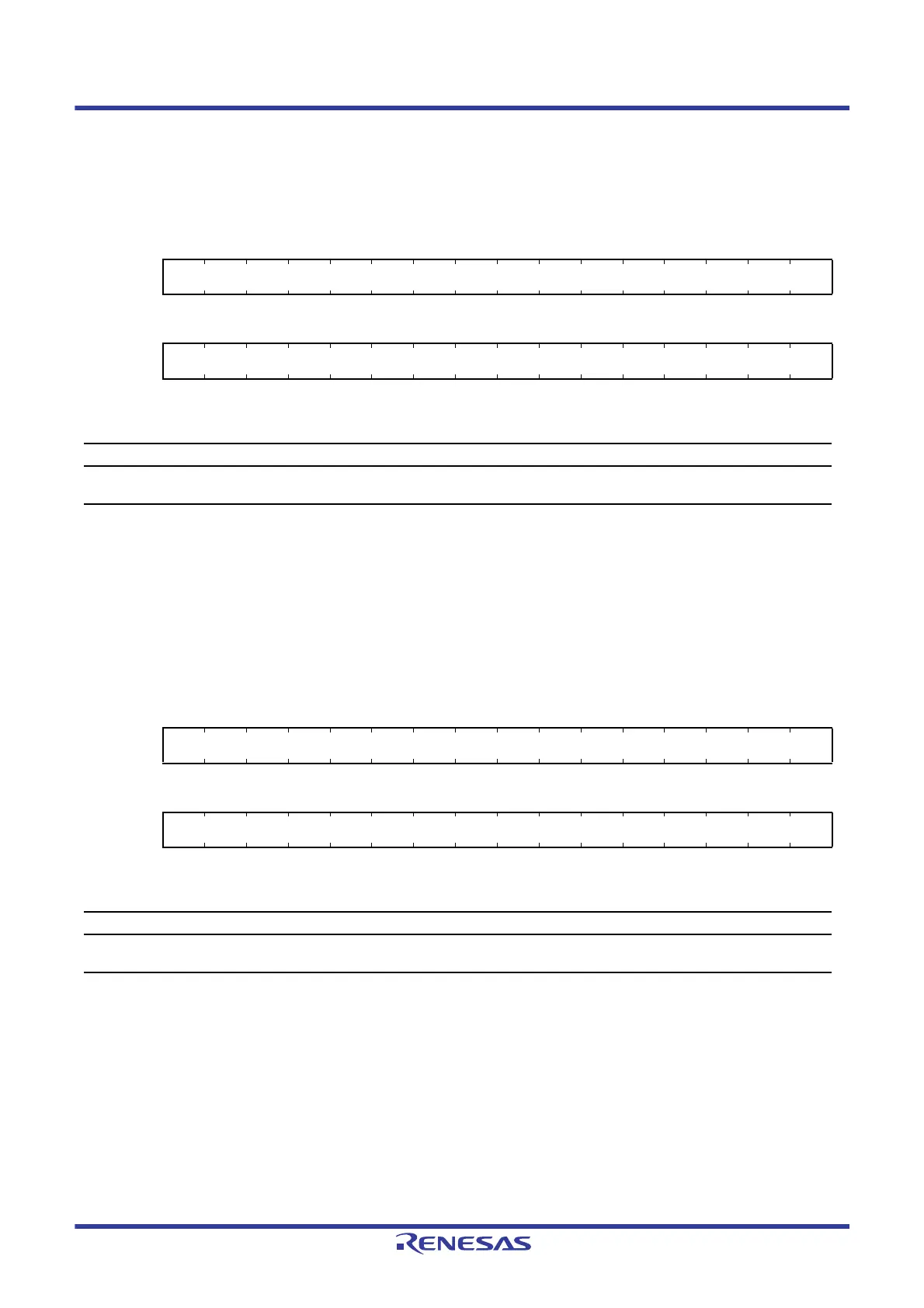

Address(es): DMAC0.DMSAR 0008 2000h, DMAC1.DMSAR 0008 2040h, DMAC2.DMSAR 0008 2080h, DMAC3.DMSAR 0008 20C0h

b31 b30 b29 b28 b27 b26 b25 b24 b23 b22 b21 b20 b19 b18 b17 b16

Value after reset:

0000000000000000

b15 b14 b13 b12 b11 b10 b9 b8 b7 b6 b5 b4 b3 b2 b1 b0

Value after reset:

0000000000000000

Bit Description Setting Range R/W

b31 to b0 Specifies the transfer source start address. 0000 0000h to 0FFF FFFFh (256 Mbytes)

F000 0000h to FFFF FFFFh (256 Mbytes)

R/W

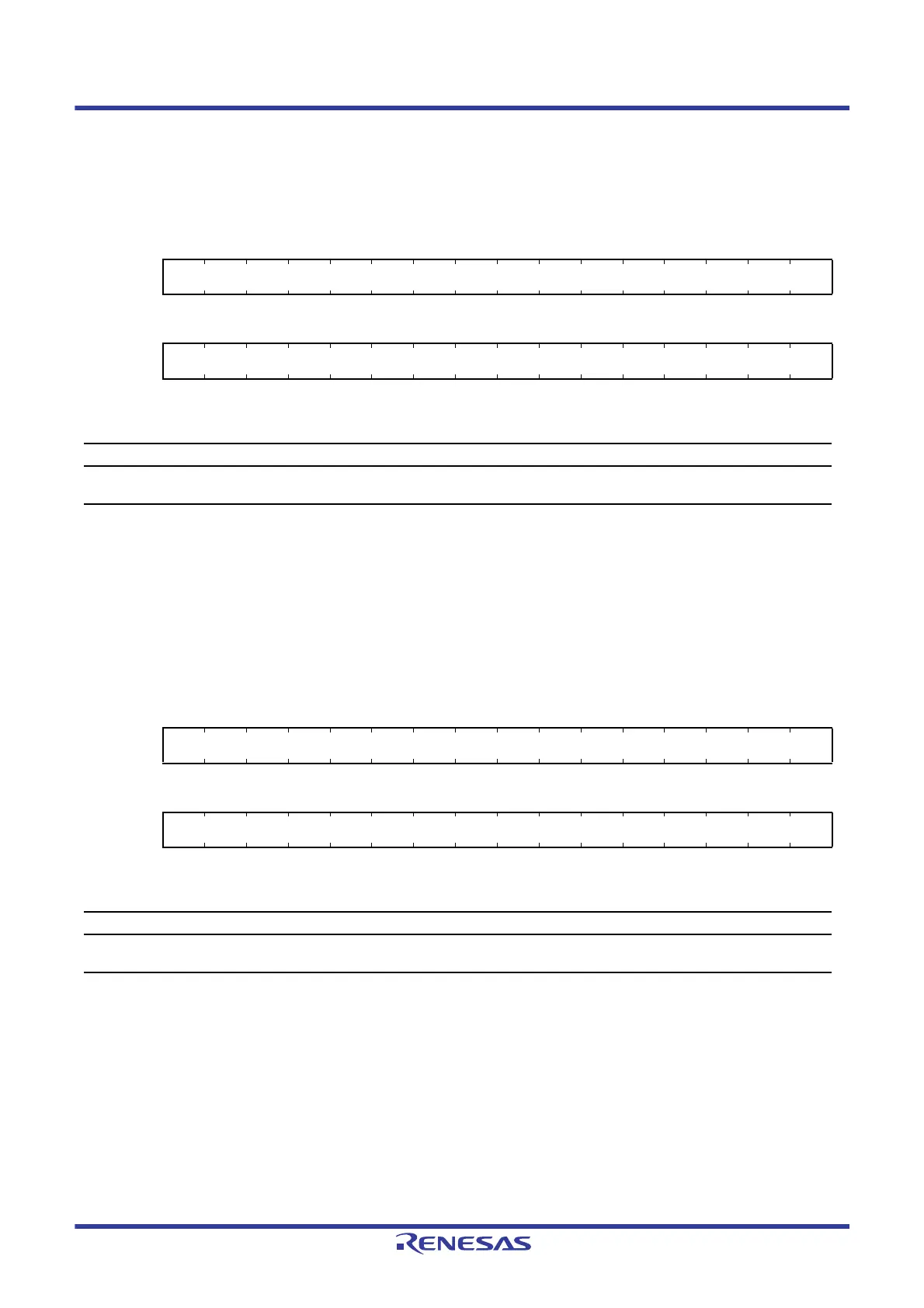

Address(es): DMAC0.DMDAR 0008 2004h, DMAC1.DMDAR 0008 2044h, DMAC2.DMDAR 0008 2084h, DMAC3.DMDAR 0008 20C4h

b31 b30 b29 b28 b27 b26 b25 b24 b23 b22 b21 b20 b19 b18 b17 b16

Value after reset:

0000000000000000

b15 b14 b13 b12 b11 b10 b9 b8 b7 b6 b5 b4 b3 b2 b1 b0

Value after reset:

0000000000000000

Bit Description Setting Range R/W

b31 to b0 Specifies the transfer destination start address. 0000 0000h to 0FFF FFFFh (256 Mbytes)

F000 0000h to FFFF FFFFh (256 Mbytes)

R/W

Loading...

Loading...