R01UH0823EJ0100 Rev.1.00 Page 1141 of 1823

Jul 31, 2019

RX23W Group 35. I

2

C-bus Interface (RIICa)

35.2.13 I

2

C-bus Bit Rate Low-Level Register (ICBRL)

ICBRL is a 5-bit register to set the low-level period of SCL clock.

It also works to generate the data setup time for automatic SCL low-hold operation (refer to

section 35.8, Automatic

Low-Hold Function for SCL

); when the RIIC is used only in slave mode, this register needs to be set to a value longer

than the data setup time

*

1

.

ICBRL counts the low-level period with the internal reference clock (IICφ) specified by the ICMR1.CKS[2:0] bits.

If the digital noise filter is enabled (the ICFER.NFE bit is 1), set the ICBRL register to a value at least one greater than

the number of stages in the noise filter. Regarding the number of stages in the noise filter, see the description of the

ICMR3.NF[1:0] bits.

Note 1. Data setup time (tSU: DAT)

250 ns (up to 100 kbps: Standard-mode (Sm))

100 ns (up to 400 kbps: Fast-mode (Fm))

Address(es): RIIC0.ICBRL 0008 8310h

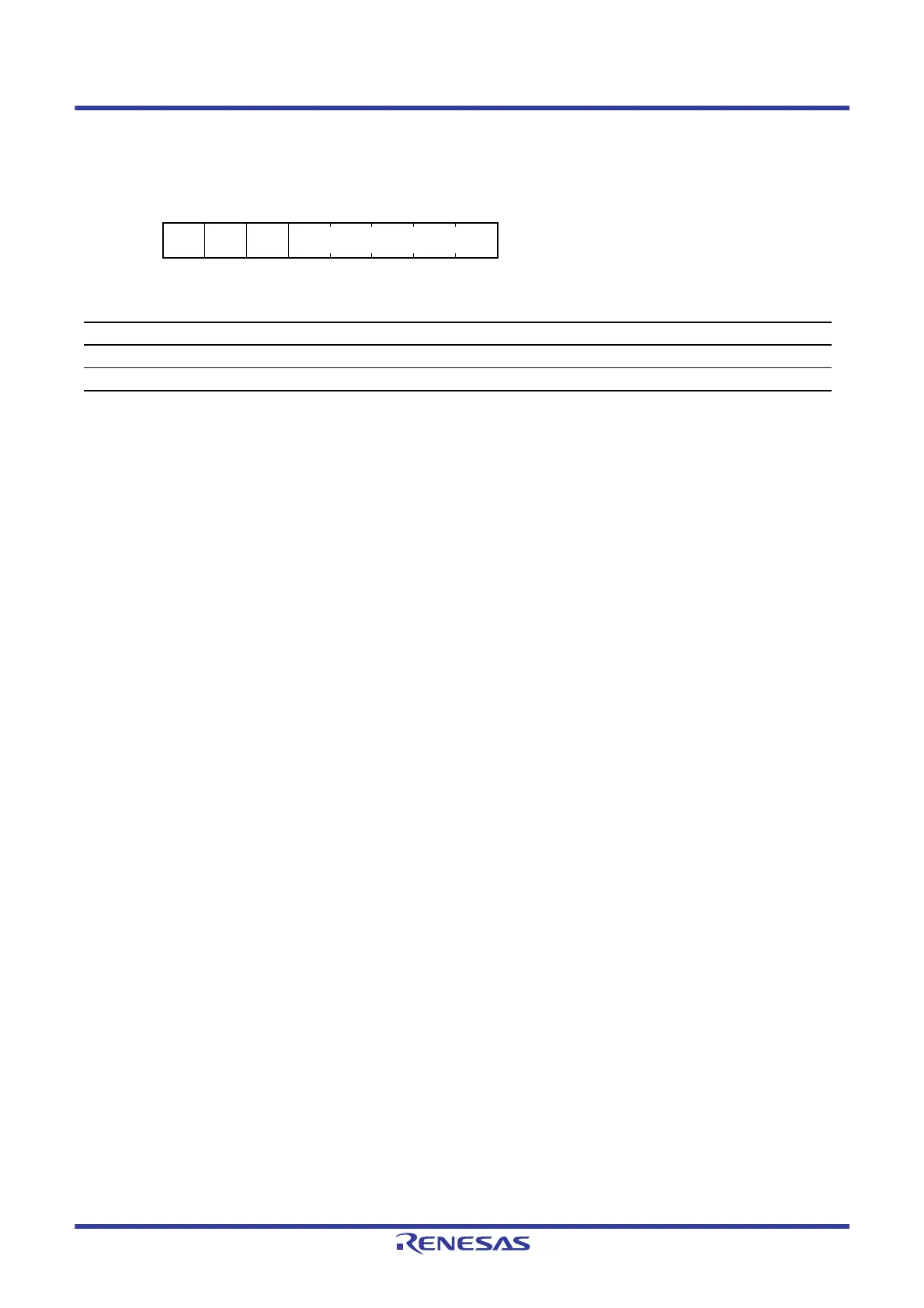

b7 b6 b5 b4 b3 b2 b1 b0

— — — BRL[4:0]

Value after reset:

11111111

Bit Symbol Bit Name Description R/W

b4 to b0 BRL[4:0] Bit Rate Low-Level Period Low-level period of SCL clock R/W

b7 to b5 — Reserved These bits are read as 1. The write value should be 1. R/W

Loading...

Loading...