R01UH0823EJ0100 Rev.1.00 Page 733 of 1823

Jul 31, 2019

RX23W Group 26. 8-Bit Timer (TMR)

26.2.4 Timer Control Register (TCR)

Note 1. To use an external counter reset signal, set the corresponding pin function. For details, refer to section 21, I/O Ports and section

22, Multi-Function Pin Controller (MPC).

Note 2. Do not choose this option for TMR0.

CCLR[1:0] Bits (Counter Clear)

Select the condition by which TCNT is cleared.

OVIE Bit (Timer Overflow Interrupt Enable)

Selects whether overflow interrupt requests (OVIn) issued by TCNT are enabled or disabled.

CMIEA Bit (Compare Match Interrupt Enable A)

Selects whether compare match A interrupt requests (CMIAn) that are issued when the value of TCORA corresponds to

that of TCNT are enabled or disabled.

CMIEB Bit (Compare Match Interrupt Enable B)

Selects whether compare match B interrupt requests (CMIBn) that are issued when the value of TCORB corresponds to

that of TCNT are enabled or disabled.

Address(es): TMR0.TCR 0008 8200h, TMR1.TCR 0008 8201h, TMR2.TCR 0008 8210h, TMR3.TCR 0008 8211h

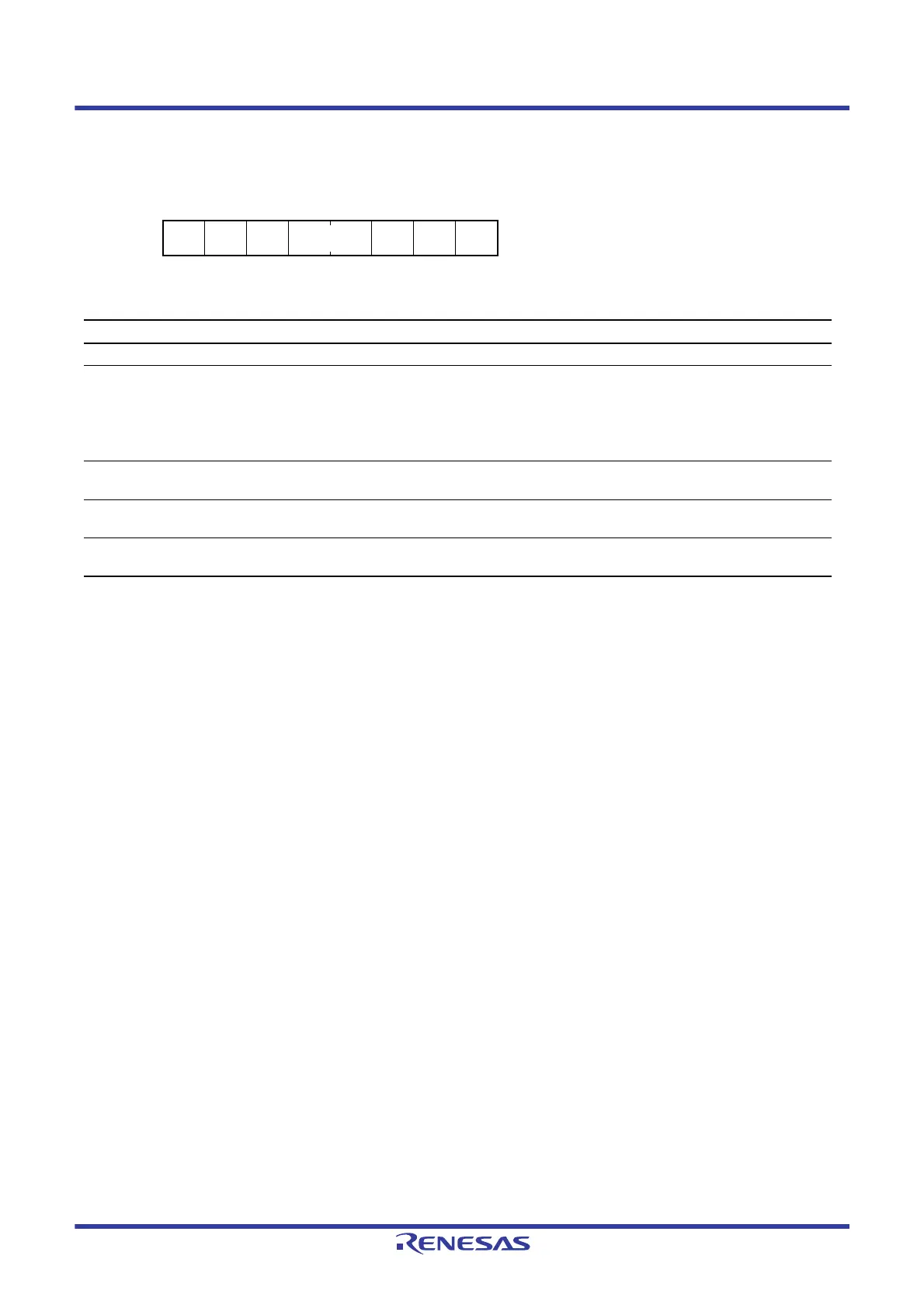

b7 b6 b5 b4 b3 b2 b1 b0

CMIEB CMIEA OVIE CCLR[1:0] — — —

Value after reset:

00000000

Bit Symbol Bit Name Description R/W

b2 to b0 — Reserved These bits are read as 0. The write value should be 0. R/W

b4, b3 CCLR[1:0] Counter Clear*

1

b4 b3

0 0: Clearing is disabled

0 1: Cleared by compare match A

1 0: Cleared by compare match B

1 1: Cleared by the external counter reset signal*

2

(Select edge or level by the TMRIS bit in TCCR.)

R/W

b5 OVIE Timer Overflow Interrupt Enable 0: Overflow interrupt requests (OVIn) are disabled

1: Overflow interrupt requests (OVIn) are enabled

R/W

b6 CMIEA Compare Match Interrupt Enable A 0: Compare match A interrupt requests (CMIAn) are disabled

1: Compare match A interrupt requests (CMIAn) are enabled

R/W

b7 CMIEB Compare Match Interrupt Enable B 0: Compare match B interrupt requests (CMIBn) are disabled

1: Compare match B interrupt requests (CMIBn) are enabled

R/W

Loading...

Loading...