R01UH0823EJ0100 Rev.1.00 Page 861 of 1823

Jul 31, 2019

RX23W Group 32. USB 2.0 Host/Function Module (USBc)

32.2.4 CFIFO Port Register (CFIFO)

D0FIFO Port Register (D0FIFO)

D1FIFO Port Register (D1FIFO)

(1) When the MBW bit is 1

(2) When the MBW bit is 0

There are three FIFO ports: CFIFO, D0FIFO, and D1FIFO. Each FIFO port is configured of a port register (CFIFO,

D0FIFO, or D1FIFO) that handles reading of data from the FIFO buffer memory and writing of data to the FIFO buffer

memory, a port select register (CFIFOSEL, D0FIFOSEL, or D1FIFOSEL) that is used to select the pipe assigned to the

FIFO port, and a port control register (CFIFOCTR, D0FIFOCTR, or D1FIFOCTR).

Each FIFO port has the following precautions.

The FIFO buffer for DCP (control transfer) should be accessed through the CFIFO port.

Accessing a FIFO buffer using DMA/DTC transfer should be performed through the D0FIFO or D1FIFO port.

The D0FIFO and D1FIFO ports can also be accessed by the CPU.

When using functions specific to a FIFO port, the pipe number (selected pipe) specified by the CURPIPE[3:0] bits

in the port select register cannot be changed (when the DMA/DTC transfer function is used, etc.).

The same pipe should not be assigned to two or more FIFO ports.

There are two FIFO buffer states: the access right for a FIFO buffer can be on the CPU side or on the Serial

Interface Engine (SIE) side. When the access right for a FIFO buffer is on the SIE side, the FIFO buffer cannot be

accessed from the CPU.

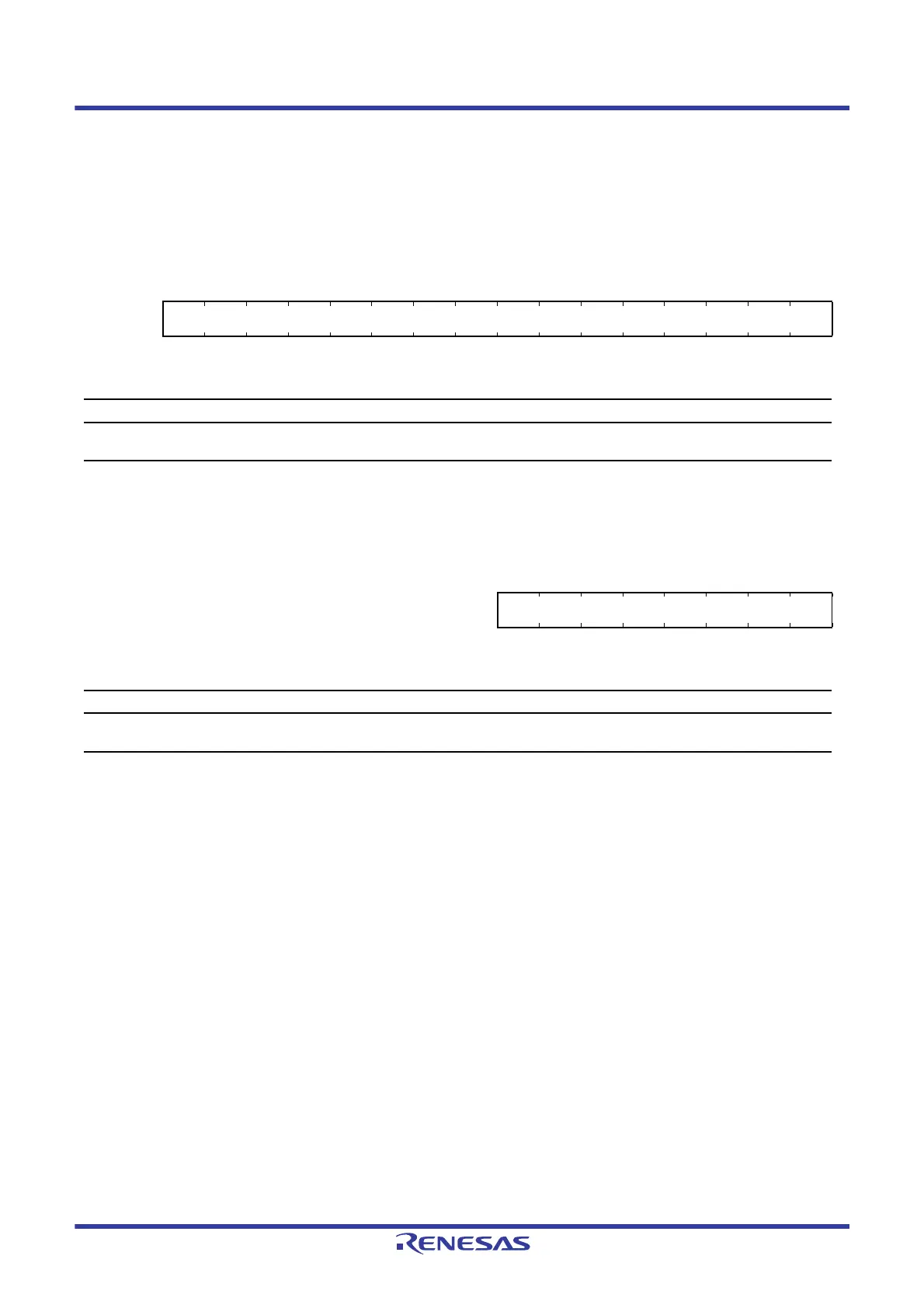

Address(es): CFIFO 000A 0014h, D0FIFO 000A 0018h, D1FIFO 000A 001Ch

b15 b14 b13 b12 b11 b10 b9 b8 b7 b6 b5 b4 b3 b2 b1 b0

Value after reset:

0000000000000000

Bit Symbol Bit Name Description R/W

b15 to b0 — FIFO Port This port is used for reading receive data from the FIFO buffer and

writing transmit data to the FIFO buffer.

R/W

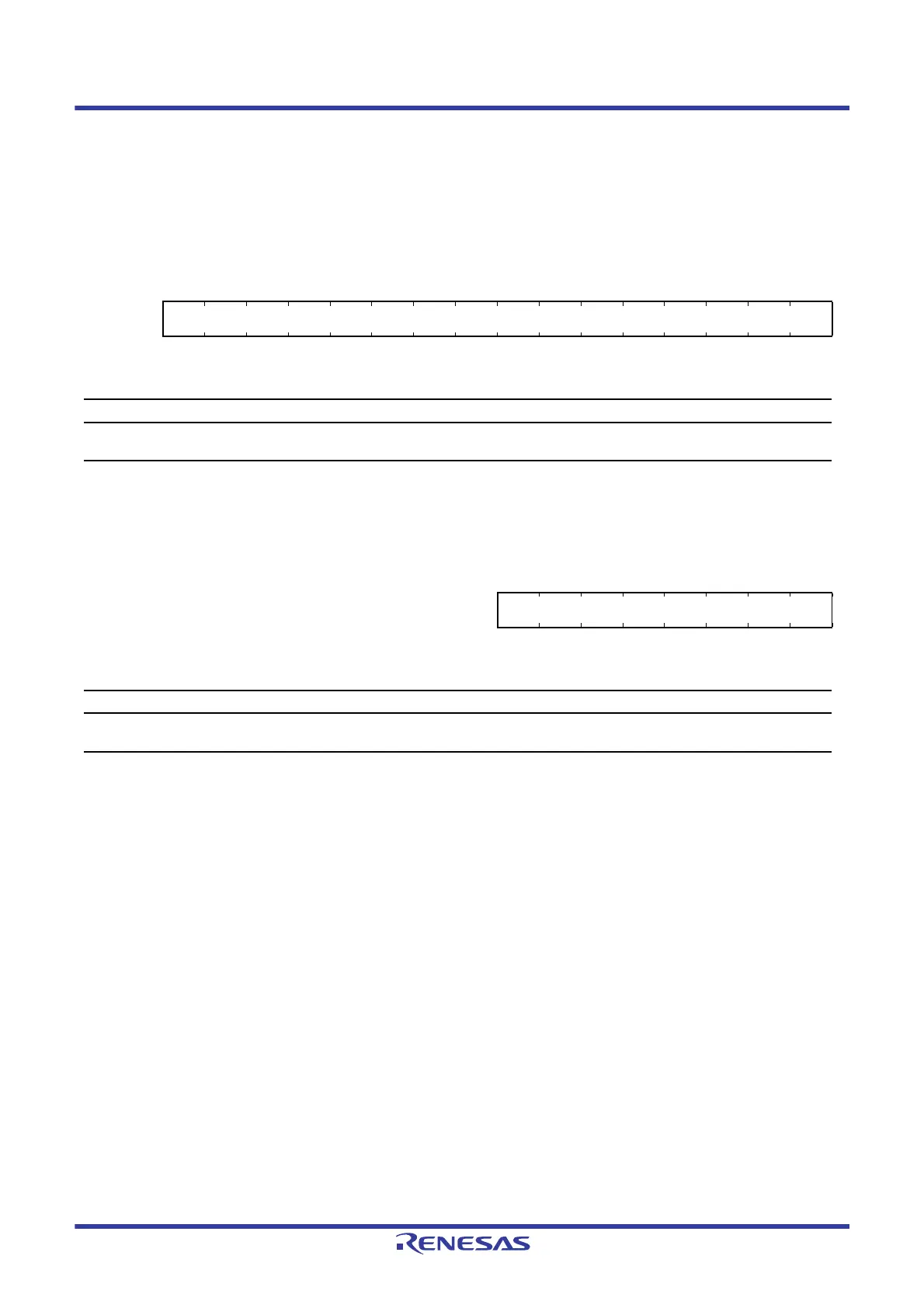

Address(es): CFIFO 000A 0014h, D0FIFO 000A 0018h, D1FIFO 000A 001Ch

b7 b6 b5 b4 b3 b2 b1 b0

L[7:0]

Value after reset:

00000000

Bit Symbol Bit Name Description R/W

b7 to b0 L[7:0] FIFO Port This port is used for reading receive data from the FIFO buffer and

writing transmit data to the FIFO buffer.

R/W

Loading...

Loading...