R01UH0823EJ0100 Rev.1.00 Page 274 of 1823

Jul 31, 2019

RX23W Group 15. Interrupt Controller (ICUb)

15.2.5 Software Interrupt Generation Register (SWINTR)

Note 1. Only 1 can be written.

SWINT Bit (Software Interrupt Generation)

When 1 is written to the SWINT bit, the interrupt request register 027 (IR027) is set to 1.

If 1 is written to the SWINT bit when the DTC transfer request enable register 027 (DTCER027) is set to 0, an interrupt

to the CPU is generated.

If 1 is written to the SWINT bit when the DTC transfer request enable register 027 (DTCER027) is set to 1, a DTC

transfer request is issued.

Address(es): ICU.SWINTR 0008 72E0h

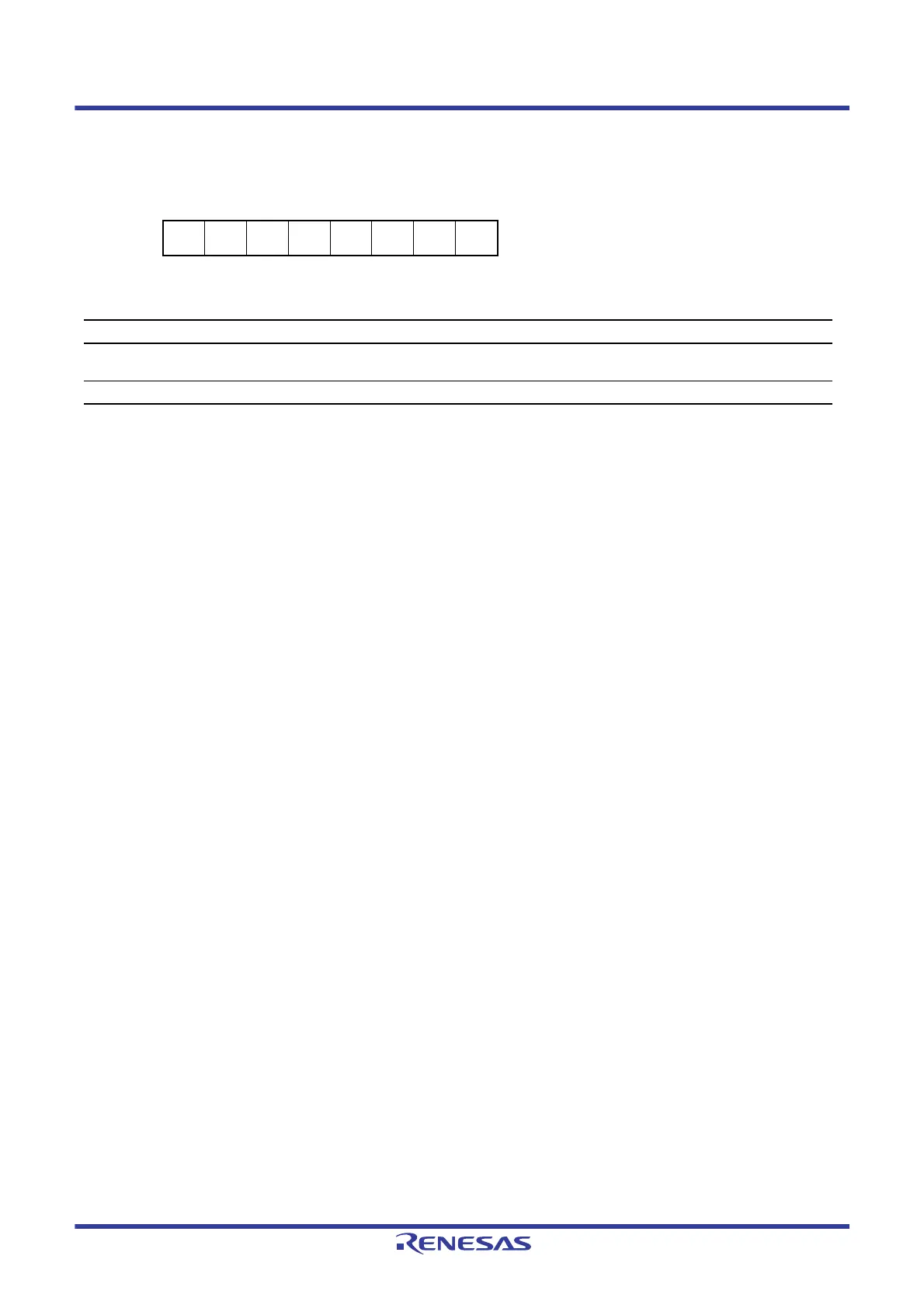

b7 b6 b5 b4 b3 b2 b1 b0

———————SWINT

Value after reset:

00000000

Bit Symbol Bit Name Description R/W

b0 SWINT Software Interrupt Generation This bit is read as 0. Writing 1 issues a software interrupt request.

Writing 0 to this bit has no effect.

R/(W)

*

1

b7 to b1 — Reserved These bits are read as 0. The write value should be 0. R/W

Loading...

Loading...