R01UH0823EJ0100 Rev.1.00 Page 664 of 1823

Jul 31, 2019

RX23W Group 25. 16-Bit Timer Pulse Unit (TPUa)

Note 1. When TGRC or TGRD is used as a buffer register, TCNT is not cleared because the buffer register setting has priority, and

compare match/input capture does not occur.

Note 2. Synchronous operation is selected by setting the TPU.TSYR.SYNCj bit (j = 0, 3) to 1.

Note 1. This bit is reserved in TPU1, TPU2, TPU4, and TPU5. This bit is read as 0. The write value should be 0.

Note 2. Synchronous operation is selected by setting the TPU.TSYR.SYNCj bit (j = 1, 2, 4, 5) to 1.

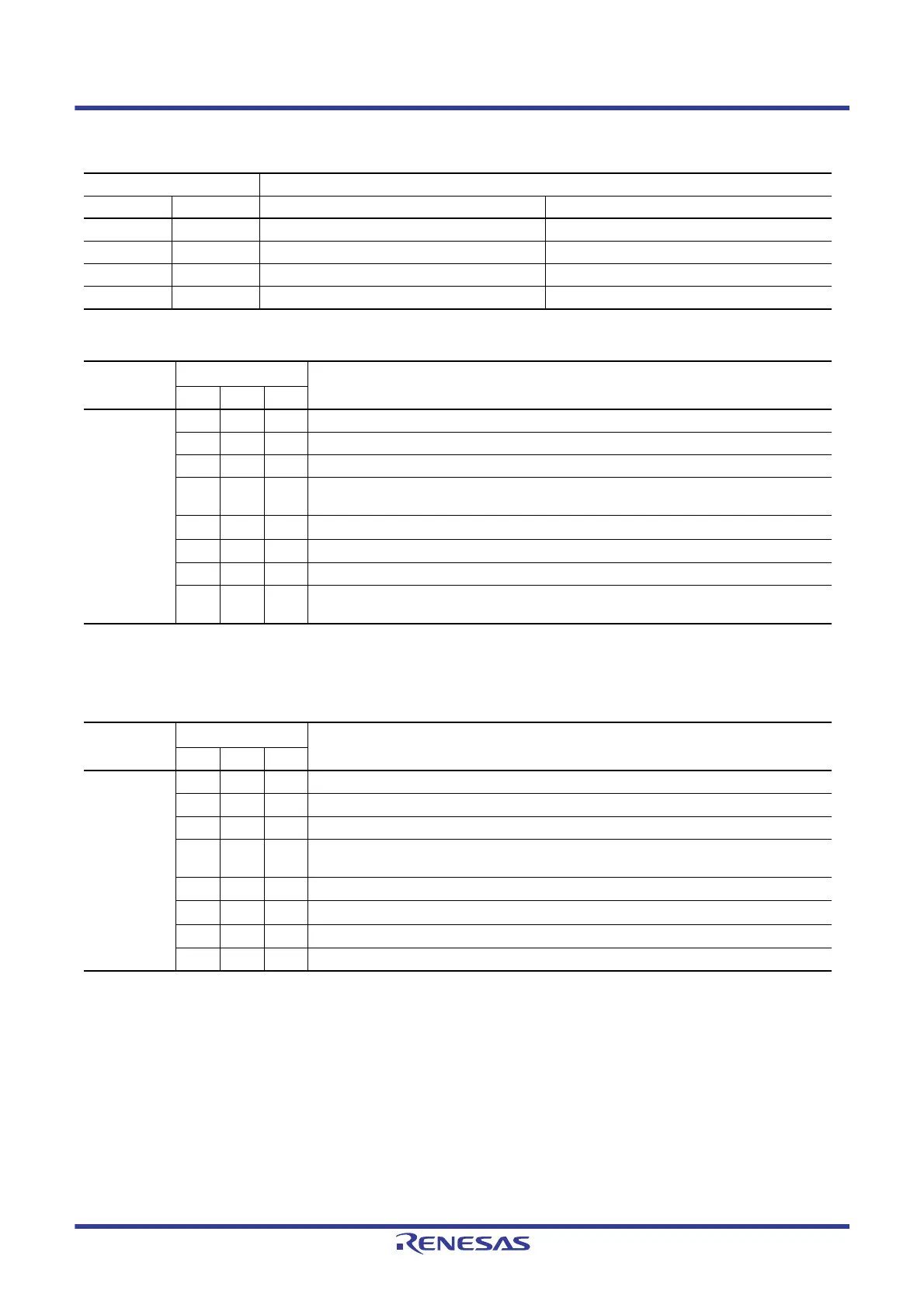

Table 25.10 Bits CKEG[1:0]

Bits CKEG[1:0] Input Clock

b4 b3 Internal Clock External clock

0 0 Counted at falling edge Counted at rising edge

0 1 Counted at rising edge Counted at falling edge

1 0 Counted at both edges Counted at both edges

1 1 Counted at both edges Counted at both edges

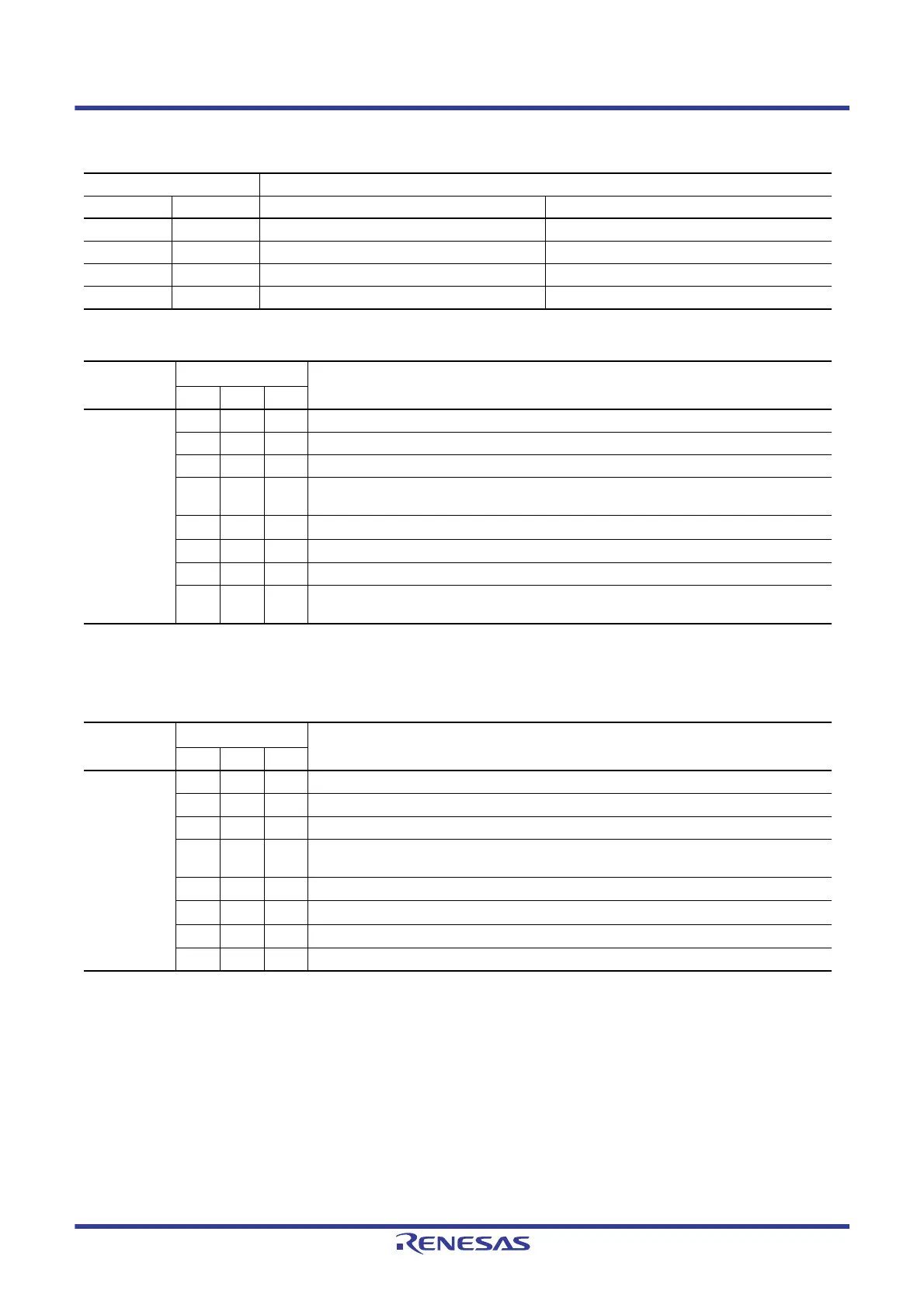

Table 25.11 Bits CCLR[2:0] (TPU0, TPU3)

Channel

Bits CCLR[2:0]

Descriptionb7 b6 b5

TPU0, TPU3 0 0 0 TCNT clearing disabled

0 0 1 TCNT cleared by TGRA compare match/input capture

0 1 0 TCNT cleared by TGRB compare match/input capture

0 1 1 TCNT cleared by counter clearing for another channel performing synchronous clearing/

synchronous operation*

2

1 0 0 TCNT clearing disabled

1 0 1 TCNT cleared by TGRC compare match/input capture*

1

1 1 0 TCNT cleared by TGRD compare match/input capture*

1

1 1 1 TCNT cleared by counter clearing for another channel performing synchronous clearing/

synchronous operation*

2

Table 25.12 Bits CCLR[2:0] (TPU1, TPU2, TPU4, TPU5)

Channel

Bits CCLR[2:0]

Descriptionb7*

1

b6 b5

TPU1, TPU2,

TPU4, TPU5

0 0 0 TCNT clearing disabled

0 0 1 TCNT cleared by TGRA compare match/input capture

0 1 0 TCNT cleared by TGRB compare match/input capture

0 1 1 TCNT cleared by counter clearing for another channel performing synchronous clearing/

synchronous operation*

2

1 0 0 Setting prohibited

1 0 1 Setting prohibited

1 1 0 Setting prohibited

1 1 1 Setting prohibited

Loading...

Loading...