R01UH0823EJ0100 Rev.1.00 Page 1349 of 1823

Jul 31, 2019

RX23W Group 38. Serial Peripheral Interface (RSPIa)

SPRDTD Bit (RSPI Receive/Transmit Data Select)

The SPRDTD bit selects whether the SPDR reads values from the receive buffer or from the transmit buffer.

If reading is from the transmit buffer, the value written to SPDR register immediately beforehand is read.

When reading the transmit buffer, do so before writing of the number of frames set in the SPFC[1:0] bits is finished and

after generation of the transmit buffer empty interrupt (While the SPSR.SPTEF flag is 1).

For details, refer to

section 38.2.5, RSPI Data Register (SPDR).

SPLW Bit (RSPI Longword Access/Word Access Specification)

The SPLW bit specifies the access width for SPDR. Access to the SPDR register in words when the SPLW bit is 0 and in

longwords when the SPLW bit is 1.

Also, when the SPLW bit is 0, set the SPCMDm.SPB[3:0] bits (RSPI data length setting bits) to 8 to 16 bits. Do not

select 20, 24, or 32 bits.

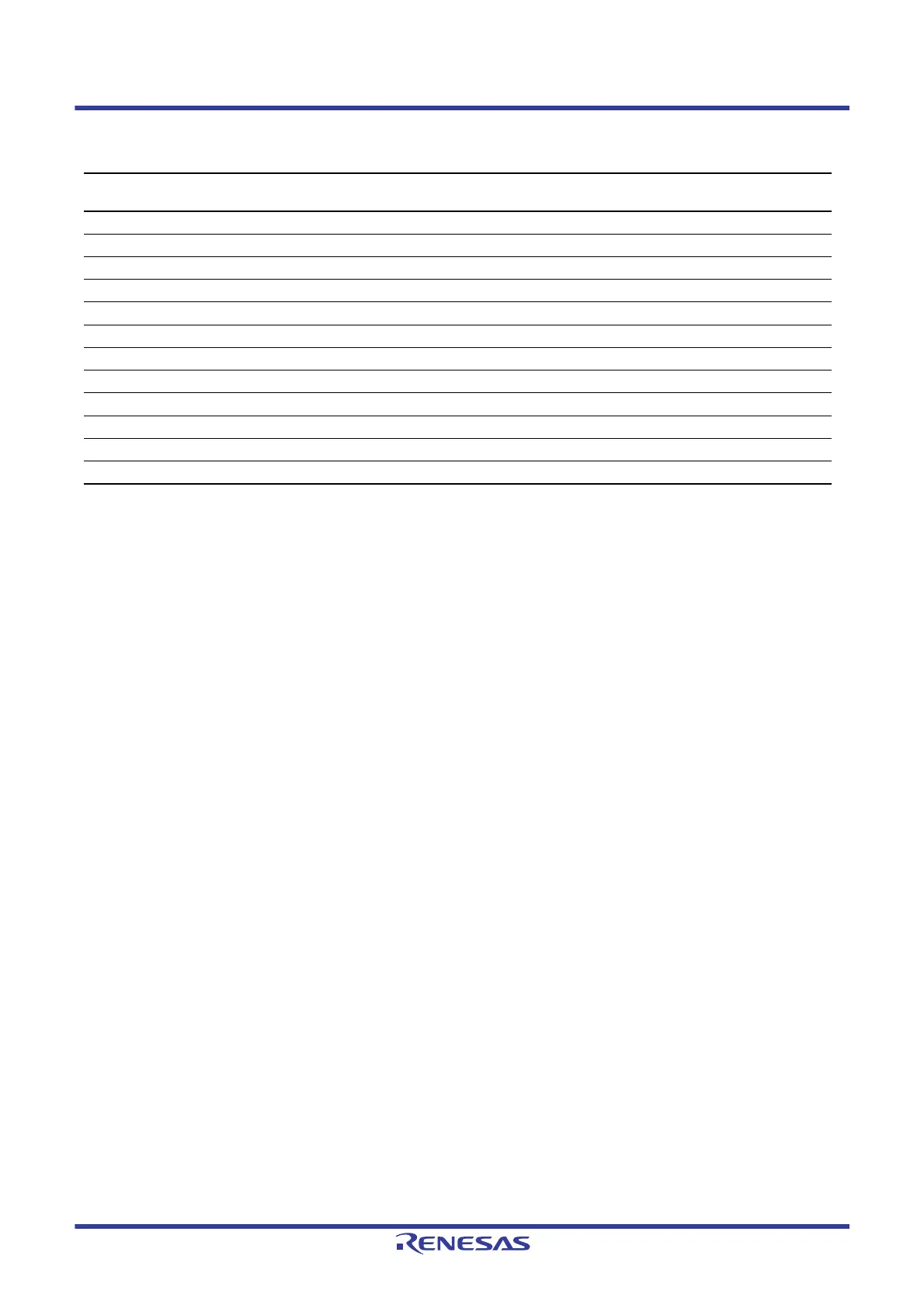

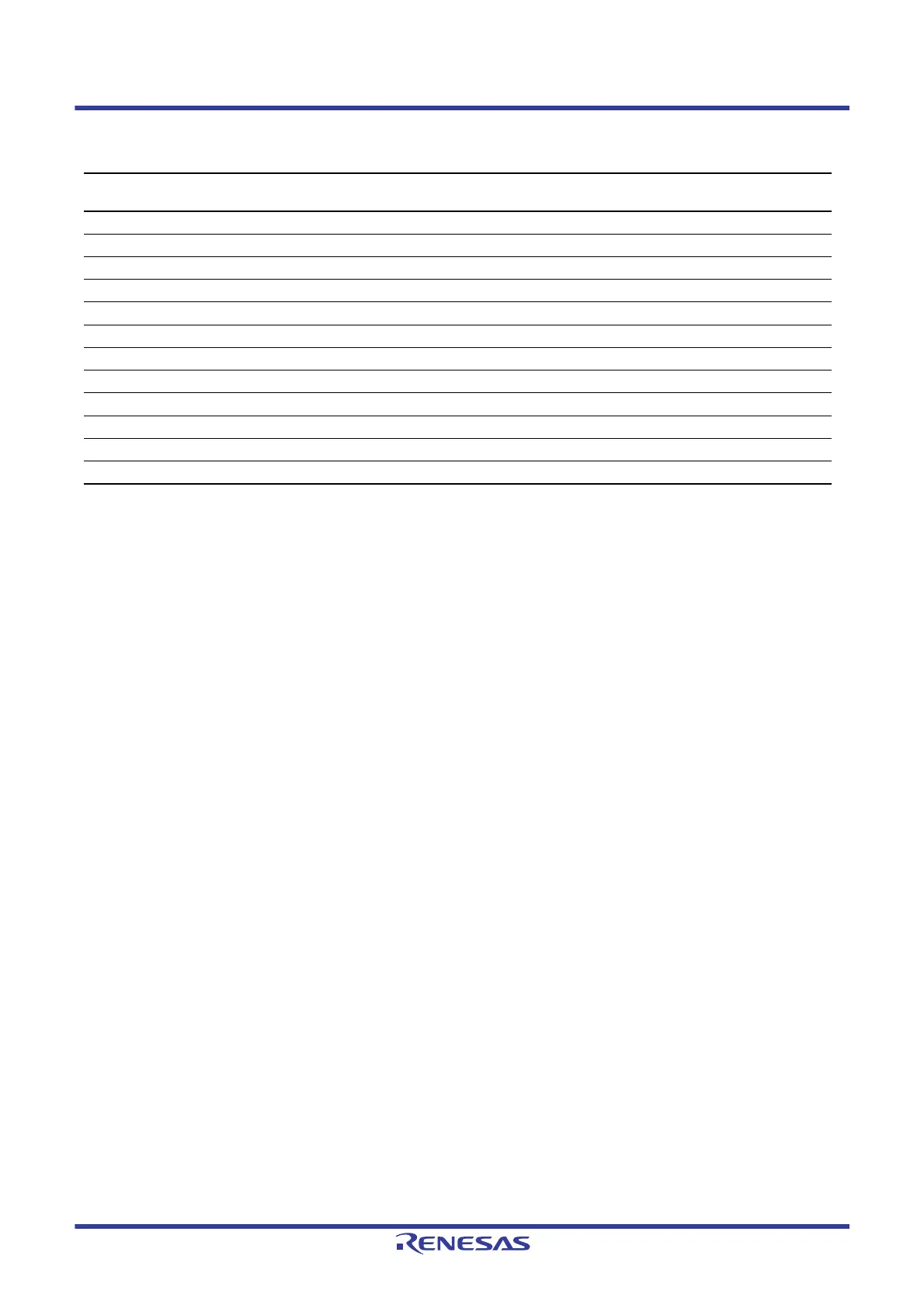

Table 38.4 Settable Combinations of SPSLN[2:0] Bits and SPFC[1:0] Bits

Setting SPSLN[2:0] SPFC[1:0]

Number of Frames in

a Single Sequence

Number of Frames at which Transmit Buffer or Receive

Buffer Status Becomes “Has Valid Data”

1-1 000b 00b 1 1

1-2 000b 01b 2 2

1-3 000b 10b 3 3

1-4 000b 11b 4 4

2-1 001b 01b 2 2

2-2 001b 11b 4 4

3 010b 10b 3 3

4011b11b4 4

5 100b 00b 5 1

6 101b 00b 6 1

7 110b 00b 7 1

8 111b 00b 8 1

Loading...

Loading...