SPORT Control Registers and Data Buffers

5-56 ADSP-21368 SHARC Processor Hardware Reference

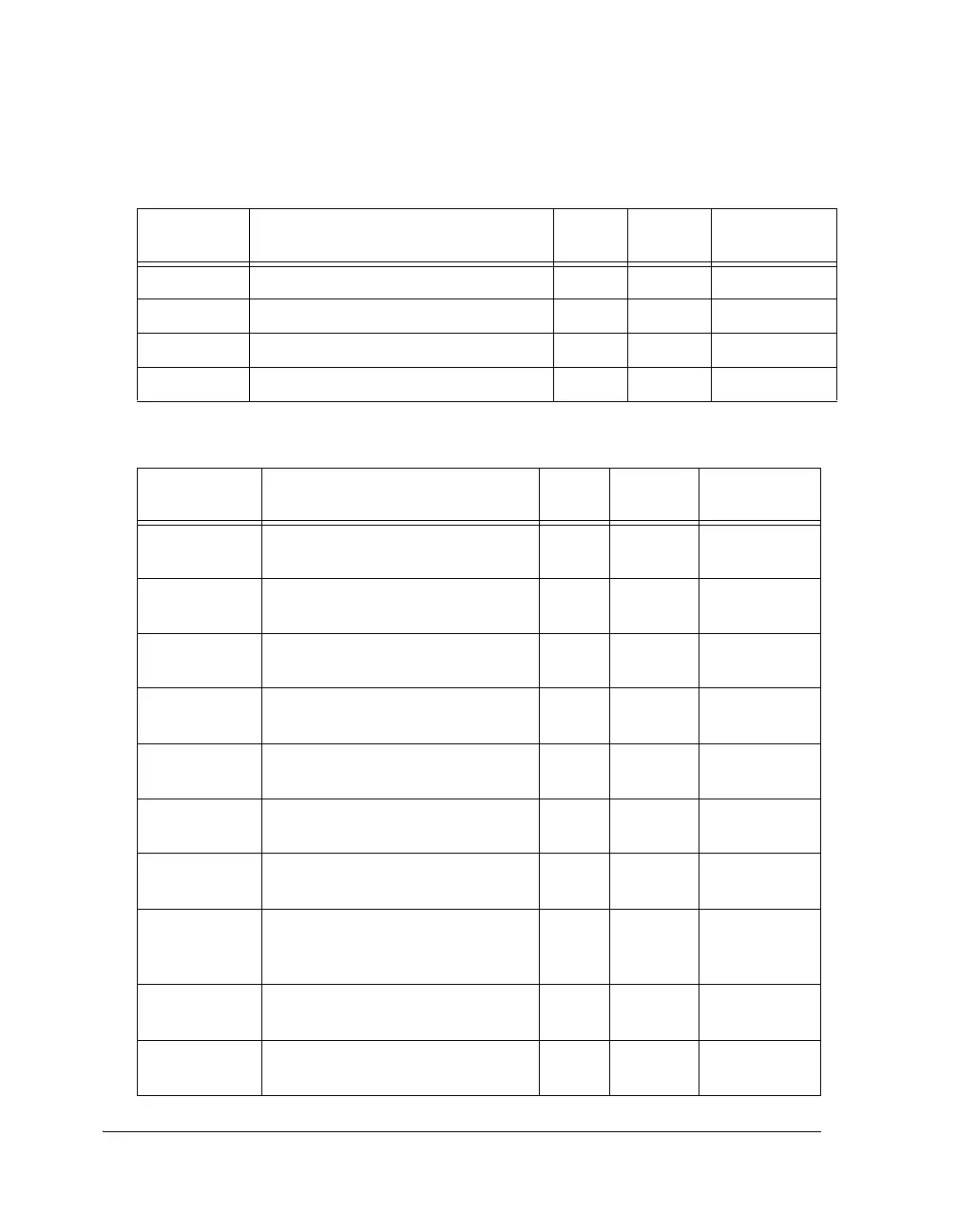

TX5A Transmitter FIFO Register in SP5A 32 1 00864

RX5A Receiver FIFO Register in SP35A 32 1 00865

TX5B Transmitter FIFO Register in SP5B 32 1 00866

RX5B Receiver FIFO Register in SP5B 32 1 00867

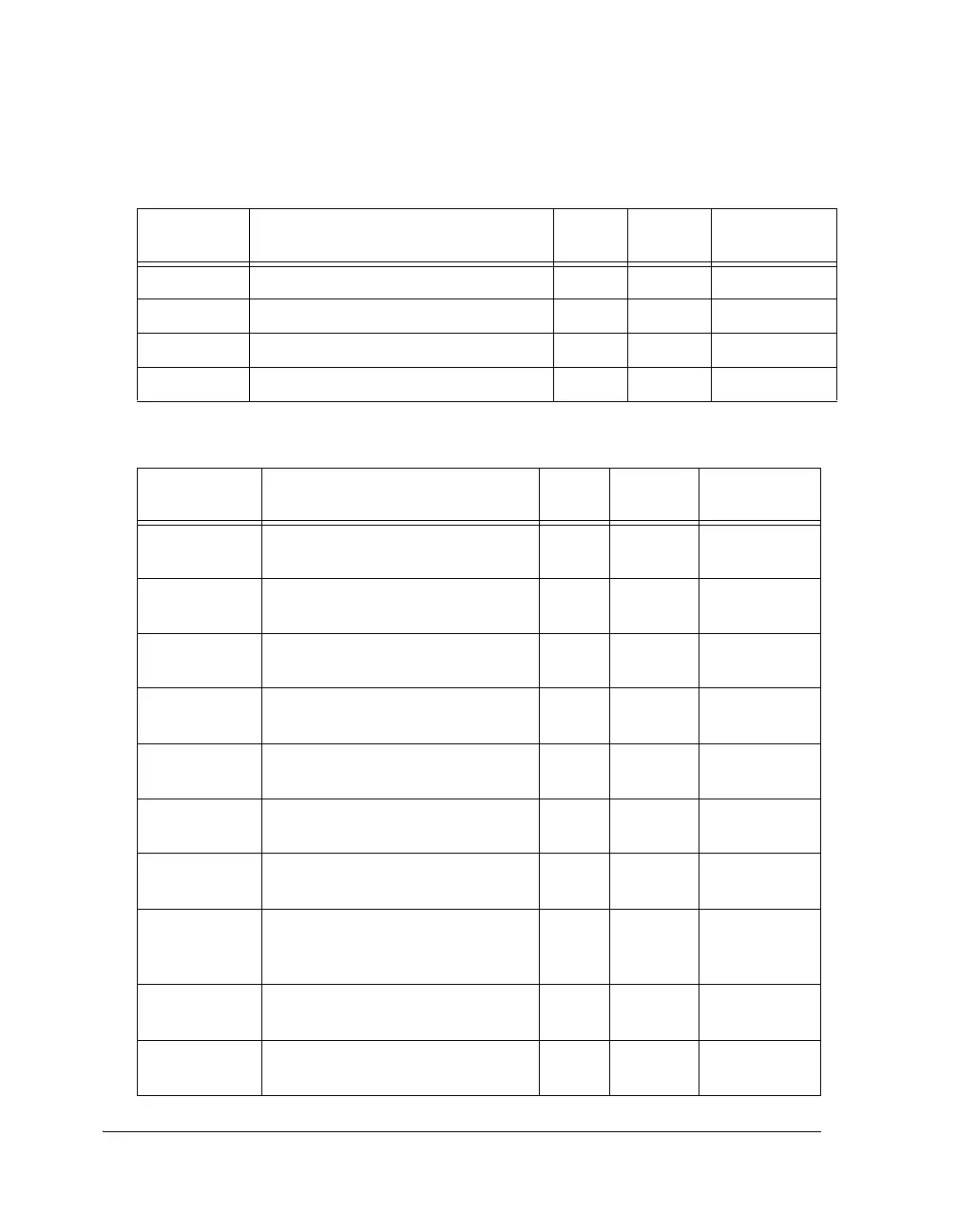

Table 5-8. SPORT6 and SPORT7 Registers

Register Name Function Width No. of

Registers

Memory Map

[17:0]

SPCTL6–7 SPORT Control Register for

SPORT6, SPORT7

32 2 04800–04801

DIV6–7 Clock and Frame Sync Divisors for

SPORT6, 7

32 2 04802–04803

SPMCTL6 SPORT Multichannel Control Regis-

ter for SPORT6

32 1 04804

SP4CS0–3 Multichannel Active channels select

for SPORT6

32 4 04807–04808

SP7CS0–3 Multichannel Active channels select

for SPORT7

32 4 04809–0480C

SP6CCS0–3 Multichannel Transmit Compand

Select (128 channels) for SPORT6

32 4 0480D–04810

SP7CCS0–3 Multichannel Receive Compand

Select (128 channels) for SPORT7

32 4 04811–04814

SPCNT6–7 Clock and Frame Sync Divider

Counter (internal use only) for

SPORT6, 7

32 2 04815–04816

SPMCTL7 SPORT Multichannel Control Regis-

ter for SPORT7

32 1 04817

SPERRCTL6–

7

SPORT Error Interrupt Control

Register for SPORT6, SPORT7

7 2 04818–04819

Table 5-7. SPORT4 and SPORT5 Registers (Cont’d)

Register

Name

Function Width No. of

Registers

Memory Map

[17:0]

Loading...

Loading...