Serial Inputs

7-6 ADSP-21368 SHARC Processor Hardware Reference

The polarity of left/right encoding is independent of the serial mode

frame sync polarity selected in IDP_SMODE for that channel (Table 7-1).

Note that I

2

S mode uses a low frame sync (left/right) signal to dictate the

first (left) channel, and left-justified sample pair mode uses a

HIGH frame

sync (left/right) signal to dictate the first (left) channel of each frame. In

either mode, the left channel has bit 3 set (= 1) and the right channel has

bit 3 cleared (= 0).

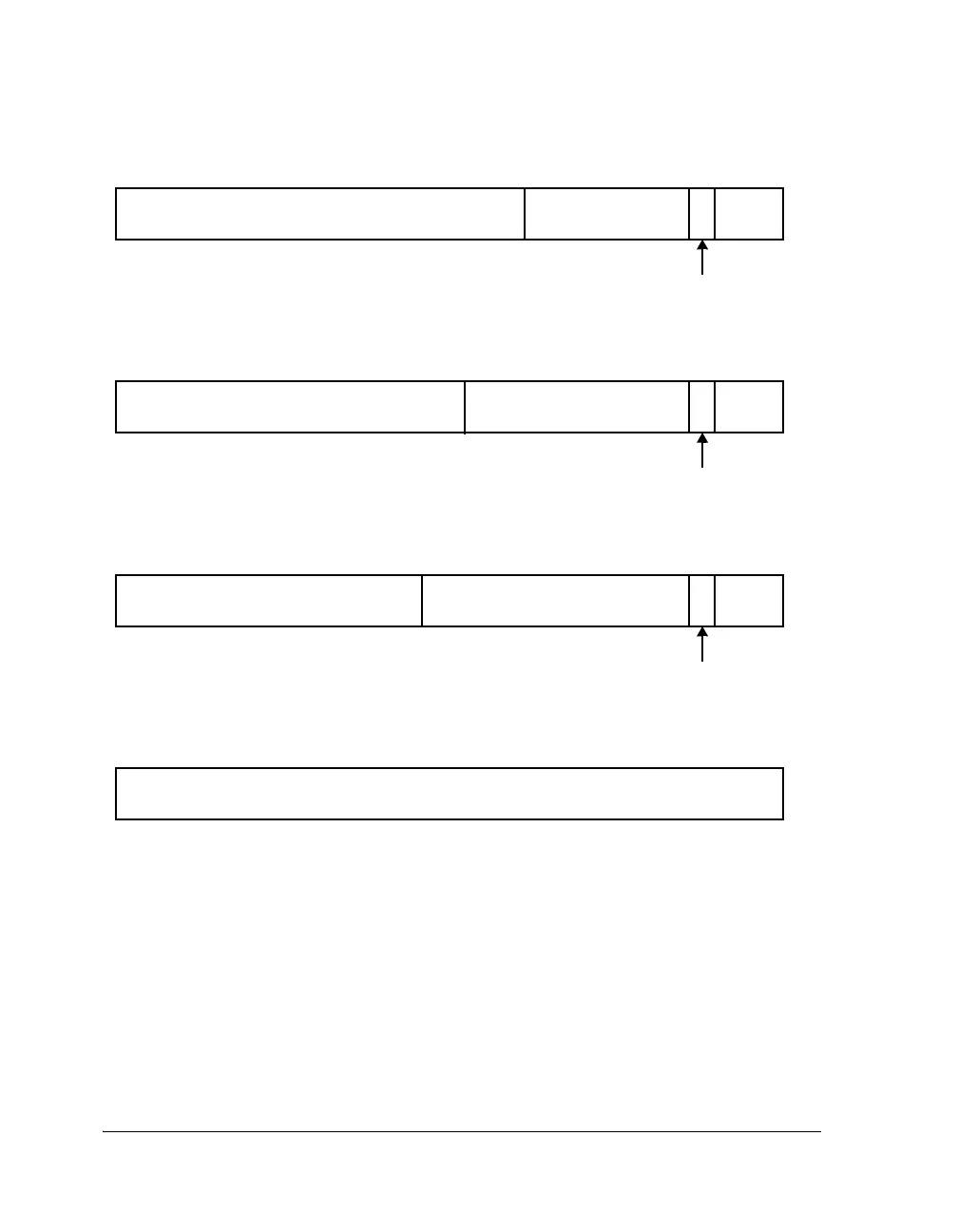

Figure 7-6. FIFO Data Packing for Right-Justified (20-Bit Data)

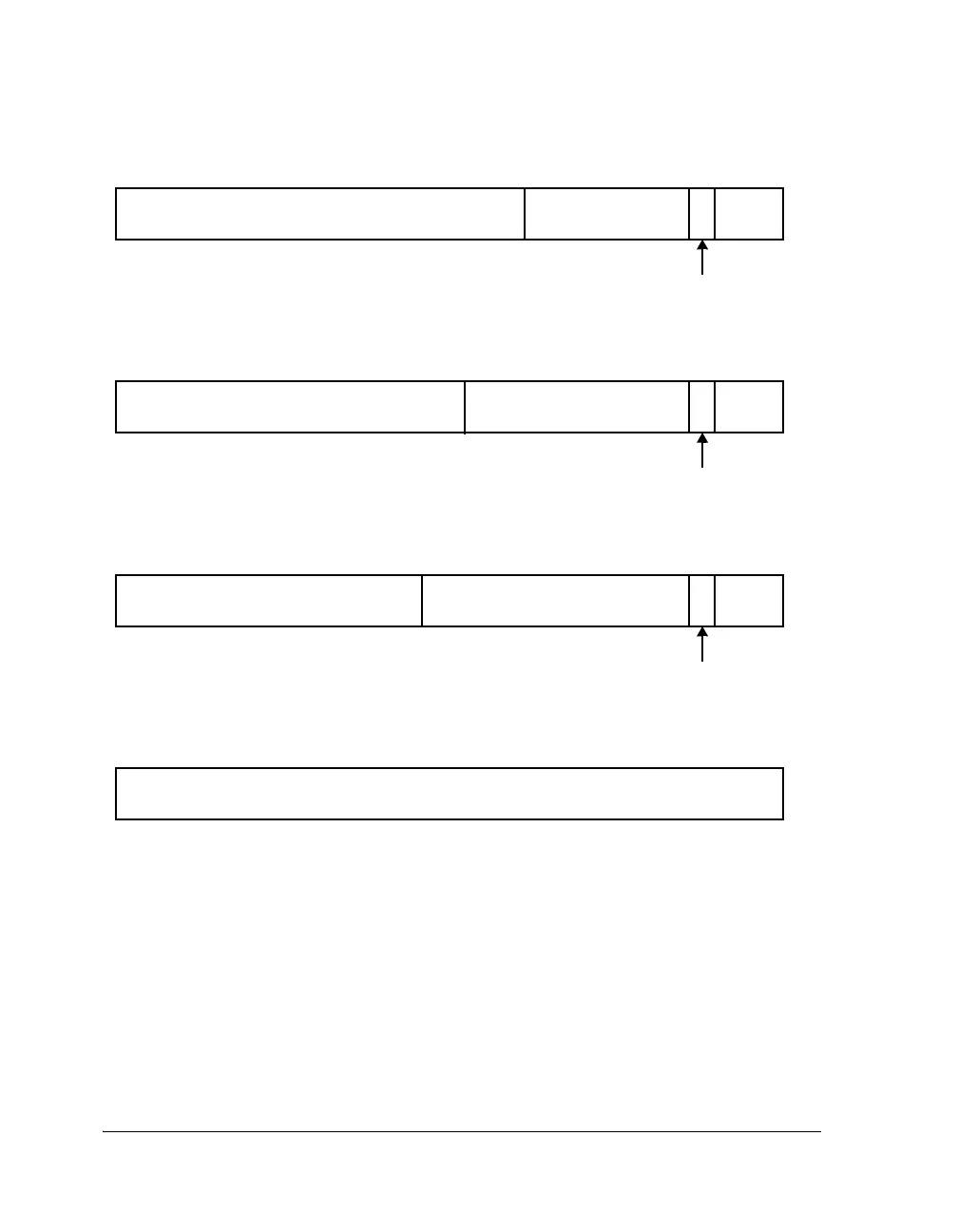

Figure 7-7. FIFO Data Packing for Right-Justified (18-Bit Data)

Figure 7-8. FIFO Data Packing for Right-Justified (16-Bit Data)

Figure 7-9. FIFO Data Packing for I

2

S and Left-Justified (32-Bit Data)

Channel

Encoding

Bits (2–0)

L/R Encoding

Spare Bits (11–4)

20-Bit

Audio

Data (31–12)

3

Set to LOW

Channel

Encoding

Bits (2–0)

L/R Encoding

Spare Bits (13–4)

18-Bit

Audio

Data (31–14)

3

Set to LOW

Channel

Encoding

Bits (2–0)

L/R Encoding

Spare Bits (15–4)

16-Bit

Audio

Data (31–16)

3

Set to LOW

16-Bit Audio Data (31–0)

Loading...

Loading...